Porozumění síle západky S-R: brána k moderní elektronice

Západky jsou jednoduchá digitální zařízení, která ukládají jeden kousek informací a udržují tuto hodnotu, dokud nedostane nové vstupní signály.Používají se v digitálních systémech k dočasnému držení binárních dat.Západky mohou být vyrobeny pomocí různých druhů základních logických bran, jako jsou a nebo ne, Nand a ani brány.Tento článek zkoumá design, funkci, variace a použití západky S-R a zdůrazňuje svou nejlepší roli v moderní elektronice a jeho použití v praktických obvodech a simulacích digitálních logických.

Katalog

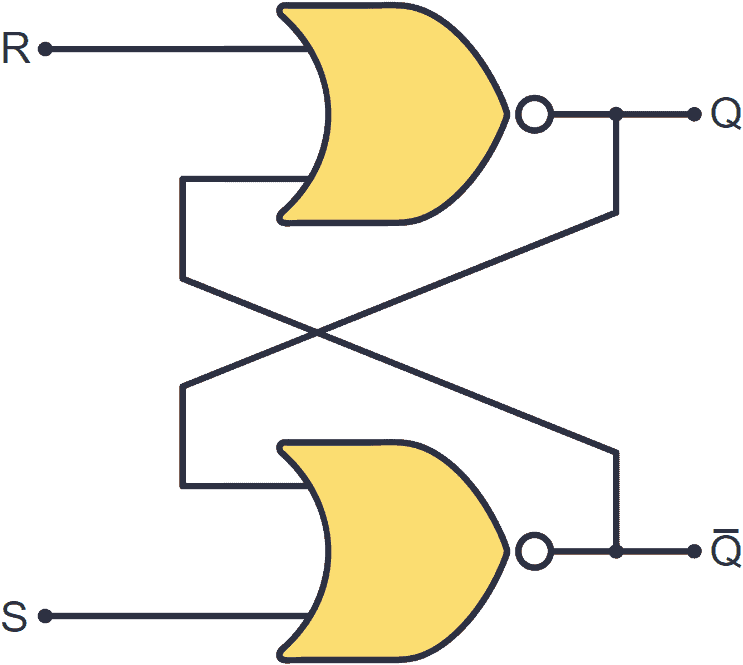

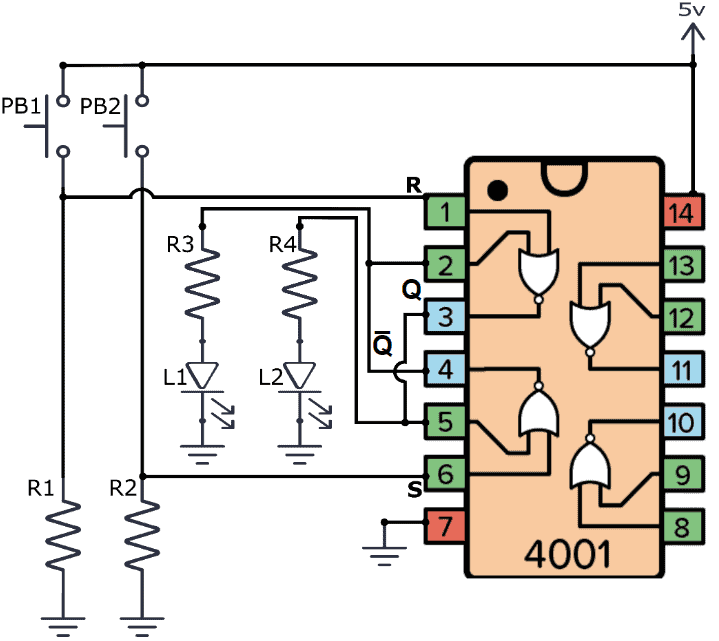

Obrázek 1: Schéma obvodu západky S-R

Struktura západky S-R

Západka S-R (Set-Reset), základní kámen v digitální elektronice, je bistabilní multivibrátor.Je schopen udržovat jeden ze dvou odlišných stabilních stavů na neurčito bez vnějšího vstupu.Tato funkce činí SR západku hlavní součástí v paměťových a přepínacích operacích napříč různými elektronickými zařízeními.

Strukturálně se západka SR skládá ze dvou propojených ani bran uspořádaných v designu zpětné vazby.Na tomto specifickém uspořádání je důležité, protože nabízí předpoklady pro bistabilitu.Výstup každé brány NOT Bran je připojen přímo ke vstupu druhého a vytváří kontinuální smyčku zpětné vazby, která podporuje operaci západky.

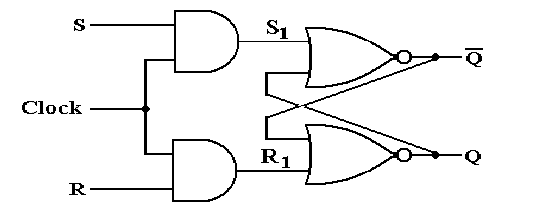

Obrázek 2: S-R západka a hodinový signál (CLK)

Při rozšiřování základního designu zavádí západka SR další vstup: hodinový signál (CLK).Toto vylepšení zahrnuje vstup hodin, který přináší vrstvu ovládání a integruje operace západky do systémů, které vyžadují synchronizaci.Tato synchronizace se zavázala, protože určuje přesné momenty, kdy může západka změnit stavy, vhodně popsané termínem „Gated“.Zahrnutí signálu hodin zajišťuje, že výstupní stav západky dochází pouze během aktivní fáze hodin, obvykle na stoupající nebo klesající hraně signálu CLK.

Zavedení vstupu CLK nejen zachovává vlastnosti základní západky SR, ale také sladí jeho provoz s časovou dynamikou větších digitálních systémů.Tato touha zarovnání po udržení integrity dat a zajištění toho, aby se přechody stavových přechodů vyskytly bez závad nebo nezamýšlených změn, zejména ve složitých konfiguracích obvodu, kde může interagovat více západků.Ovládáním, když západka reaguje na příkazy set a resetování, může se systém vyhnout problémům, jako jsou podmínky rasy a další chyby související s načasováním, které by jinak mohly narušit stabilitu a výkon systému.

Operační stavy západky S-R

Jeho provoz závisí na vstupních vstupech dvou řídicích signálů: sady a resetování (R).Zde vysvětlujeme, jak tyto vstupy ovlivňují výstupy a stavy SR západky.

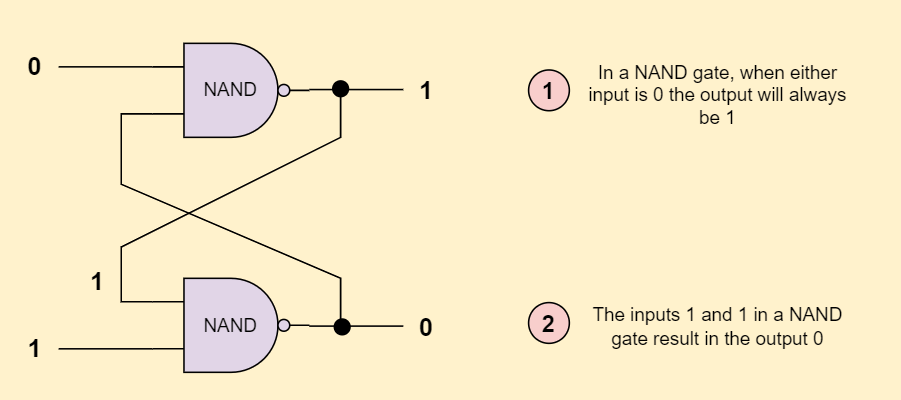

Případ 1: Nastavte podmínku

Když je vstup sady vysoký (1) a vstup resetova (R) je nízký (0), západka vstoupí do stavu nastavení.V tomto stavu bude brána NAND připojená ke vstupu R, protože vysoký vstup ze S. Tento nízký signál způsobí, že druhá brána NAND vydá vysoký signál, nastaví Q na vysokou (1) a q-bar nastavení q na vysokou (1) a q-barna nízké (0).Tento stav je stabilní a bude udržovat Q vysoký, dokud se vstupy nezmění, což ukazuje na schopnost západky ukládat vysoký stav.

Obrázek 3: Stav nastavení

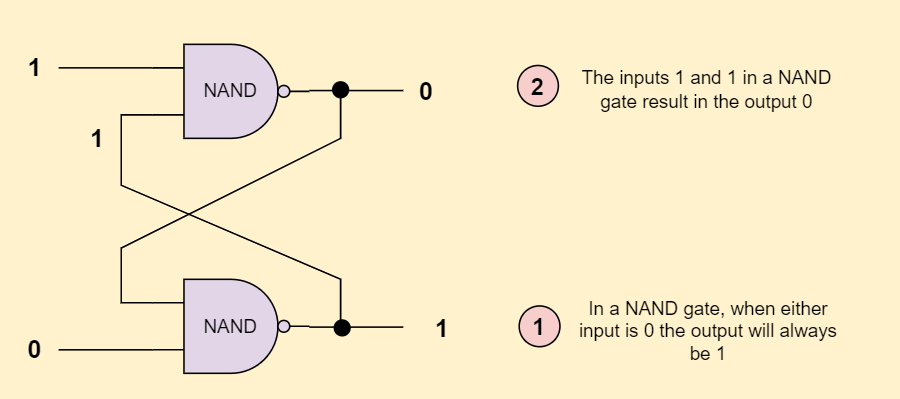

Případ 2: Obnovení stavu

Když je S nízký (0) a R je vysoký (1), západka vstupuje do resetovacího stavu.Zde je vysoký vstup na R a nízký vstup na S, aby se brána NAND připojila k výkonu R nízký signál.Tento nízký signál nastavuje Q na nízký (0) a q-bar na vysokou (1) a účinně resetuje západku.To ukazuje schopnost západky vrátit se ke stabilnímu nízkému stavu v Q, když je dána správné vstupy.

Obrázek 4: Stav resetování

Případ 3: Neplatný stav

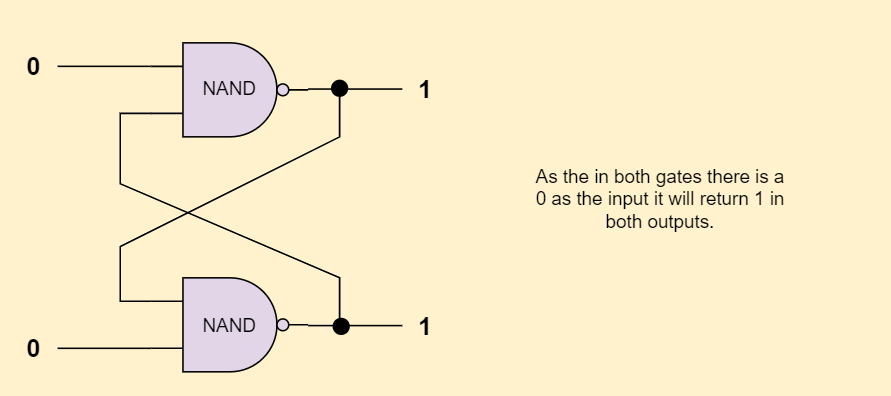

Pokud jsou oba S a R nízké (0), jsou oba vstupy do bran NAND nízké, což způsobuje, že oba výstupy Q a Q-bar stoupnou.Tento stav se nazývá neplatný nebo zakázán, protože porušuje základní pravidlo, že Q a Q-Bar by měly být vždy protiklady.Tento scénář zdůrazňuje omezení západky SR a zdůrazňuje důležitost vyhýbání se takovým nestabilním státům prostřednictvím správného řízení vstupů.

Obrázek 5: Neplatný stav

Případ 4: Podržení podmínky

Pokud jsou oba vstupy vysoké (1), výstupy závisí spíše na předchozím stavu západky než na aktuální vstupy.Toto je známé jako podmínka držení, kde Q a Q-Bar zůstávají nezměněny a zachovávají poslední platný stav západky.U některých aplikací je důležité být schopen udržovat uzavřený stav po dlouhou dobu bez úpravy, jako jsou buňky ukládání paměti, kde je integrita dat vysoce důležitá.

Obrázek 6: Stav držení

S-R západka s tabulkou pravdy

Tato tabulka není jen teoretickým nástrojem, ale je také praktická jak pro návrháře obvodů, tak pro studenty.Pomáhá jim vidět, jak se západka chová za mnoha podmínek.Níže uvádíme komplexní tabulku pravdy pro západku SR, po kterém následují vysvětlení a praktické poznatky pro každou podmínku.

|

S |

R |

Q |

Q-bar |

STÁT |

|

0 |

0 |

1 |

1 |

Neplatný |

|

0 |

1 |

0 |

1 |

Resetovat |

|

1 |

0 |

1 |

0 |

Soubor |

|

1 |

1 |

Q |

Q-bar |

Držet |

Graf 1: SR

Tabulka pravdy

Vysvětlení každého řádku

Stav podmínka (S = 1, r = 0): Tento řádek ukazuje, že když je S vysoký a R je nízký, q je nastaven na vysokou (1) a q-bar na nízký (0).To odráží odezvu obvodu na příkaz SET a účinně ukládá „1“.

Obnovení podmínky (S = 0, R = 1): Zde vstupy označují operaci resetování.V důsledku toho se Q resetuje na nízký (0) a q-bar je nastaven na vysokou (1).Tento stav ukazuje schopnost západky vrátit se k „0“.

Neplatný stav (S = 0, R = 0): Oba výstupy se v tomto stavu stávají vysokým, což se obecně vyhýbá, protože to vede k tomu, že oba výstupy jsou identické.To může vést k nestabilitě nebo nedefinovanému chování v západce, protože to porušuje pravidlo, že Q a Q-Bar by měly být vždy protiklady.

Podmínka podržení (S = 1, r = 1): V tomto scénáři si západka udržuje svůj předchozí stav a představuje jeho schopnost držet poslední nastavený stav, pokud není výslovně přikázáno změnit se.

Praktické poznatky a tipy

Porozumění výstupům: Vždy pamatujte, že Q a Q-Bar jsou v ideálním případě.Jakákoli odchylka od tohoto pravidla (jak je vidět v neplatném stavu) naznačuje problém nebo nesprávnou konfiguraci.

Vyhýbání se neplatnému stavu: Je nezbytné, aby návrháři starali zabránit situaci, ve které jsou S a R nízké.Implementace dalších logických nebo blokování může pomoci předcházet tomuto stavu.

Využití stavu držení: Podmínka držení může být zvláště výhodná v aplikacích vyžadujících zachování dat v průběhu času.Udržování integrity dat může záviset na zajištění toho, aby západka nebyla neúmyslně vstoupena do stavu sady nebo resetování.

Interpretace tabulky pravdy: Při navrhování nebo ladění obvodů odkazujte na tabulku pravdy, abyste předpovídali, jak změny vstupu ovlivní výstup, zejména ve složitých obvodech, kde se používá více západků.

Funkční dynamika západky S-R

Západka S-R (Set-Reset) funguje dobře, pouze pokud jsou její vstupy správně spravovány.Chcete-li pochopit, jak funguje, musíte vědět, jak různé vstupní kombinace ovlivňují výstupy, q a q-bar (opak q).

Obrázek 7: S-R západka

Pokud jsou jak sady), tak resetování (r) aktivovány současně (s = 1 a r = 1), západka jde do „zakázaného stavu“, kde jsou oba výstupy, q a q-bar, 0.To je problém, protože normálně by Q a Q-Bar by měly být protiklady.

Za normálních podmínek, pro nastavení západky, aktivujete S (set s na 1) a deaktivujete r (set r na 0).Díky tomu je Q vysoká (1) a Q-Bar Gone Low (0), což ukazuje, že západka může uložit 1. Chcete-li resetovat západku, aktivujete r (set r na 1) a deaktivujete S (sada S na 0).Díky tomu je Q jít nízko (0) a Q-Bar Go High (1), ukazující západku se může vyčistit a uložit 0.

Když jsou oba vstupy deaktivovány (s = 0 a r = 0), západka udržuje svůj poslední stav, buď nastavený nebo resetováním.To je dobré pro ukládání dat nebo udržování stavu bez nutnosti nepřetržitého vstupu.

Podmínky závodu mohou komplikovat operaci západky S-R.K těmto chybám dojde, když se výstupy silně spoléhají na načasování změn vstupu, což vede k nepředvídatelným výsledkům, pokud se vstupy změní téměř ve stejnou dobu.Aby tomu zabránilo a zajistilo, že západky pracují spolehlivě, často se používají mechanismy časového zpoždění.Tato zpoždění zajišťují, že jeden vstup se aktivuje poté, co druhý má čas na stabilizaci.Aby byla západka použita v digitálních obvodech, kde je vyžadováno přesné načasování, musí provádět důsledně a udržovat stabilní výstupy.To je umožněno kontrolovaným načasováním.

Logický diagram západky S-R

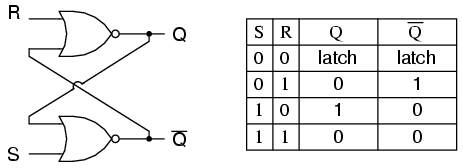

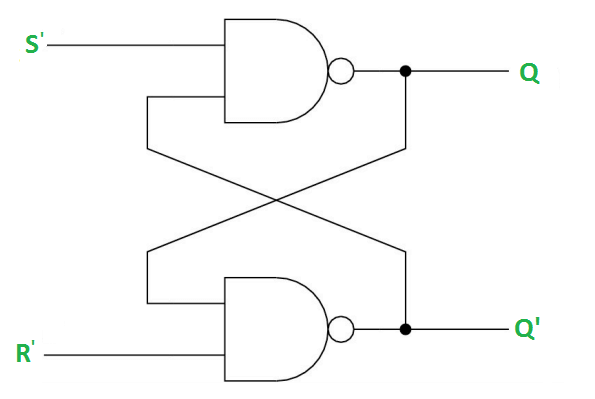

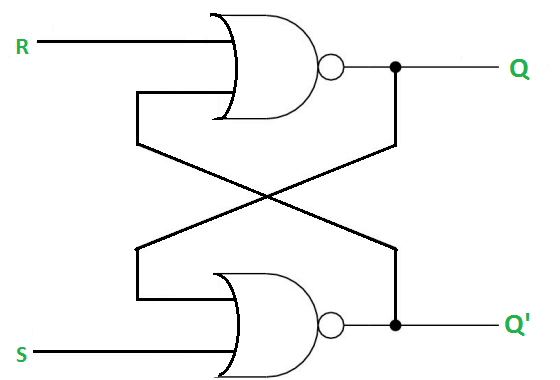

Západka SR je základní sekvenční logický obvod se dvěma hlavními konfiguracemi: Nor nebo Nand Gates.Každé nastavení ovlivňuje to, jak západka funguje a reaguje na vstupy, což umožňuje přizpůsobení pro různé elektronické aplikace.

Obrázek 8: Logický diagram představuje západku S-R pomocí brány NAND

Implementace pomocí NAND Gates

Při stavbě západky SR s Nand Gates se k udržení jeho stavu používá zpětná vazba.Toto nastavení umožňuje, aby západka udržovala svůj předchozí stav, když jsou oba vstupy (S a R) nízké.Nand Gates vysoko, pokud oba vstupy nejsou vysoké.Stav západky se změní, když je jeden vstup vysoký a druhý je nízký.Nejlepší je vyhnout se nastavení S a R vysokého současně, protože to nutí oba výstupy klesnout, což vede k nedefinovanému stavu, kdy výstupy již nejsou doplňkové.Správné řízení vstupů je nutností zabránit nestabilitě v SR západkách založených na NAND.

Implementace pomocí ani brány

Použití ani brány pro západku SR mění provozní podmínky ve srovnání s Nand Gates.V této konfiguraci drží západka svůj stav, když jsou oba vstupy vysoké.Západka mění stav, když je jeden vstup nízký a druhý je vysoký.Ani brány nevystupují vysoko, pouze pokud jsou oba vstupy nízké.Toto nastavení je užitečné v obvodech, kde má výchozí stav mít oba výstupy nízký, což zajišťuje předvídatelný výstup za podmínek s vysokým vstupem.Nejlepší je však vyhnout se nastavení obou vstupů nízkého zároveň, protože to způsobuje protichůdné výstupy a snižuje spolehlivost západky.

Obrázek 9: Logický diagram představuje západku S-R pomocí nebo brány

Příklad obvodu

Zkoumání toho, jak SR západky fungují v reálném životě, ukazuje jejich užitečnost.Dobrým příkladem je obvod používající čip CD4001, který má čtyři ani brány.Tento obvod ukazuje, jak mohou západky SR ovládat zařízení, jako jsou LEDS, pomocí jednoduchých akcí, jako je stisknutí tlačítek.

V tomto příkladu jsou nastaveny brány NOR v čipu CD4001, aby vytvořily západku SR.Dvě brány jsou připojeny ve smyčce zpětné vazby, aby se udržel stav západky.Klashbuttons se přidávají do obvodu jako vstupy pro nastavení a resetování.Stisknutím tlačítka změní stav vstupu, který mění západku a stav LED.Například stisknutí tlačítka sady rozsvítí LED a zůstává osvětleno i po uvolnění tlačítka, což ukazuje, jak může západka udržovat stav.

Aby se obvod zlepšil, lze přidat více LED LED, aby se ukázalo výstupní stav q a q-bar.Díky tomu je snazší vidět, jak západka funguje, což je velmi užitečné při učení.

Obrázek 10: S-R západka pomocí čipu CD4001

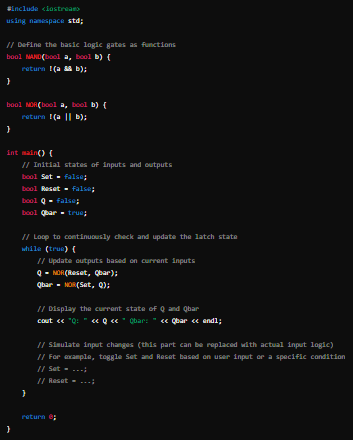

Implementace kódu

Převedení operační logiky západky SR do softwaru ukazuje, jak může digitální logický design fungovat jak v hardwaru, tak ve virtuálních simulacích.Použití programovacího jazyka, jako je C ++, je efektivní, protože podporuje komplexní logiku a kontrolu potřebnou k napodobování hardwarového chování.

Chcete -li vytvořit západku SR v C ++, začnete definováním základních logických bran jako funkcí, které fungují jako jejich hardwarové verze.Například funkce NAND Gate by na jejích vstupů vrátila opak a operace.Podobně by funkce NOR NOR brána vrátila opak operace OR.S těmito základními funkcemi můžete modelovat chování SR Latch vytvořením smyčky zpětné vazby mezi těmito funkcemi brány na základě diagramu obvodu západky.

Kód by obvykle měl smyčku, která nepřetržitě kontroluje stavy vstupů (set a resetování) a odpovídajícím způsobem aktualizuje výstupy (q a q-bar).Podmíněné příkazy uvnitř této smyčky určují, jak změny ve vstupu ovlivňují výstupy, což úzce napodobuje fyzické chování SR západky.Například, pokud jsou vstupy nastavení i resetování nízké, výstupy zůstanou stejné.Pokud je nastavena vysoká a resetová je nízká, výstup q se stává vysokým a q-bar je nízký, replikuje podmínku sady západky.

Zde je jednoduchý příklad toho, jak by to mohlo vypadat v kódu:

Obrázek 11: SR západka v C ++

Tento kód nastaví jednoduchou západku SR pomocí bran a nepřetržitě kontroluje a aktualizuje stav západky na základě vstupů.

Aplikace západky SR

Řídicí systémy v motorických operacích: Západka SR vyžadovaná systémy pro řízení motoru.Pomocí přepínačů spuštění (S) a zastavení (R) tlačítka SR udržuje motor spuštěn i po uvolnění spuštění.Toto nastavení zajišťuje, že motor běží nepřetržitě, dokud se nezastaví, což zvyšuje bezpečnost a pohodlí.

Uložení paměti a dat: Při vytváření větších obvodů paměti hraje SR západka roli, protože může ukládat jeden kousek dat.Udržuje data ve stabilním stavu, dokud není aktualizována, a vytváří základ paměťových buněk v digitálním výpočtu.

Řízení a správa signálu: V aplikacích kontrolních signálů drží SR západky specifické bity, dokud nejsou splněny určité podmínky, což zajišťuje správnou sekvenci a načasování operací.Přesnost zpracování signálu a toku dat na tom závisí.

Vodnící obvody: Západky SR stabilizují signály z mechanických spínačů a tlačítek, což zabraňuje falešným spuštěním a chybám způsobené „odskokem“, když jsou přepínače stisknuty.To je zvláště vhodné v digitálních rozhraních, jako jsou klávesnice.

Základní prvky v digitálních systémech: Návrh žabků a čítačů, které jsou vhodné pro načasování a sekvenování v elektronice, se silně spoléhá na SR západky.Používají se také jako pulzní západky pro rychlé přepínání státu.

Specializované aplikace: V asynchronních systémech se pro bezpečný a spolehlivý přenos dat používají variace, jako je západka D.V synchronních dvoufázových systémech snižují západky dat počet tranzitů, zlepšují účinnost a snižují zpoždění.

Širší důsledky v elektronice: Západky SR se široce používají v obvodech s hradlováním na elektřinu a hrají roli v úsporách energie v elektronických zařízeních.Spravují energetické státy na podrobné úrovni a přispívají k celkové energetické účinnosti digitálních systémů.

Závěr

Západka S-R ukazuje význam jednoduchých logických struktur ve složitých digitálních systémech.Při pohledu na její různá nastavení a na to, jak to funguje, vidíme, že západka S-R udržuje data stabilní a činí systémy efektivní a spolehlivé.Může fungovat za různých podmínek, které jsou uvedeny v tabulkách pravdy a logických diagramů, což je přizpůsobivé pro několik použití, od řízení motoru po základní digitální obvody, jako jsou žabky a čítače.Západka S-R je vhodná v mnoha praktických aplikacích, jako jsou paměťové buňky v počítačích a libovolné obvody v digitálních rozhraních, zvyšování účinnosti a snižování chyb v elektronických zařízeních.S mechanismy zpětné vazby a pečlivou správou vstupních signálů je západka S-R dobrá pro navrhování spolehlivějších a efektivnějších digitálních systémů.Studium své funkce prostřednictvím softwarových simulací pomáhá propojit teoretickou elektroniku s aplikacemi v reálném světě, díky čemuž je S-R západka důležitým tématem pro nové i zkušené elektronické inženýry.

Často kladené otázky [FAQ]

1. Jaký je účel západky SR?

Západka SR se používá k uložení jednoho kousku dat;Je to základní forma paměti v digitálních obvodech.Jeho hlavní funkcí je udržet stav trochu, dokud se nezmění vstupní signály.

2. Je SR západka aktivní vysoká nebo nízká?

Západka SR je obvykle aktivní vysoká, což znamená, že reaguje na vysoké vstupy (logická úroveň 1).Když jsou vstupy S (set) a R (resetování) vysoké, vyvolávají změny ve výstupu.

3. Jaká je nevýhoda s západkou SR?

Hlavní nevýhodou západky SR je její náchylnost k neplatnému stavu, kdy jsou vstupy nastavení i resetujte současně vysoké.Tato situace vede k nedefinovanému výstupu, což může vést k nespolehlivému nebo nepředvídatelnému chování.

4. Jaká jsou pravidla pro západku SR?

Pokud je S (set) vysoký a R (resetování) je nízký, výstup q je nastaven na vysokou.

Pokud je r vysoký a S je nízký, je výstup q resetován na nízký.

Pokud jsou oba S a R nízký, výstup si zachová svůj předchozí stav.

Pokud jsou S a R vysoké, je výstup nedefinovaný nebo neplatný.

5. Co je to paměť v SR Latch?

Paměť v západce SR odkazuje na jeho schopnost udržovat výstupní stav (vysoký nebo nízký) na neurčito, dokud neobdrží vstup ke změně stavu.Díky tomu je to bistabilní zařízení, ideální pro jednoduché paměťové úložiště.

6. Jaké jsou výstupy západky SR?

Západka SR má dva výstupy, Q a Q '(Q-BAR).Q představuje současný stav, zatímco Q 'je inverzní Q. Když je q vysoký, q' je nízký a naopak.

7. Kde používáme západku?

Pokud je vyžadováno krátkodobé ukládání dat nebo udržení stavu, jsou použity západky v různých druzích aplikací.To zahrnuje ukládání dat v žabkách, registrech a paměťových jednotkách, jakož i v systémech vyžadujících synchronizaci dat a funkce držení obvodu.