Zvládnutí SR Západky: Symboly, funkce a praktické aplikace

Západka SR je asynchronní obvod, který pracuje nezávisle na hodinových signálech, což z něj činí všestranný nástroj v různých aplikacích.Udržuje binární stav - buď vysoký (1) nebo nízký (0) - a může ukládat jeden kousek informací, které drží, dokud nové vstupní signály diktují změnu.Tento základní prvek binárního úložiště je konstruován pomocí dvou křížových logických bran, obvykle ani nebo NAND bran.Vstupy nastavení aktivují západku a nastaví výstup (q) na vysokou, zatímco resetovací vstup (R) nastavuje výstup na nízký.Simultánní vysoké signály na obou vstupních vstupech však musí návrháři podmínek vyhnout.Západky SR nejsou jen teoretické konstrukty;Jsou implementovány v praktických systémech pro držení dočasných údajů, podpory výsledků meziproduktu a dokonce spravování detekce chyb v kritických aplikacích, jako jsou letecké a zdravotnické prostředky, což ukazuje na jejich nezbytnost v návrhu digitálního obvodu.Katalog

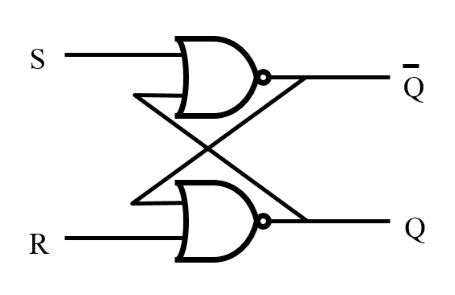

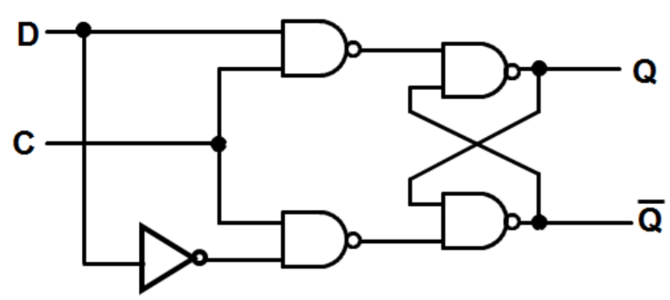

Obrázek 1: SR západka

Co je západka SR?

Západka SR, nebo nebo západka setu, je základní binární úložný prvek, který patří do kategorie asynchronních obvodů.Na rozdíl od synchronních obvodů fungují západky SR bez signálu s hodinami a spoléhají pouze na přímou kontrolu vstupních signálů.To jim umožňuje fungovat samostatně v digitálních obvodech.Západka SR může udržovat dva stabilní stavy: vysoké (1) a nízké (0), což jí umožňuje ukládat jeden kousek informací, dokud neaktualizují nové vstupní signály.

Konstrukce západky SR obvykle zahrnuje dvě křížové logické brány, běžně ani brány nebo NAND bran.V designu západkové západky SR s použitím ani brány je výstup každé brány připojen k vstupu druhého a vytváří zpětnou vazbu.Tato konfigurace zajišťuje, že západka může rychle měnit stavy na základě vstupních signálů při zachování stability, dokud nový vstup nezmění.

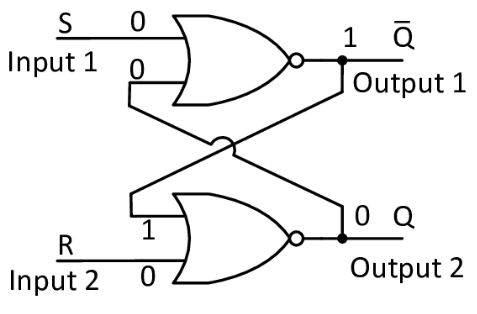

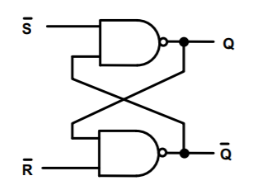

Obrázek 2: Západka SR (2)

Nastavit vstupy: Když jsou aktivovány nastavené vstupy (vstupy) (vysoký), přepne výstup západky (1).

Resetovací vstup (R): Když je aktivován vstup resetování (R) (vysoký), výstup (Q) se přepne na nízkou (0).

Oba vstupy vysoké: Pokud jsou oba vstupy S a R současně, západka vstupuje do nedefinovaného stavu, kterému by se mělo při navrhování vyhnout.

Západky SR jsou nezbytné pro dočasné ukládání dat a mezilehlé výsledky v digitálních systémech.Jsou to základní prvky ve složitějších sekvenčních obvodech, jako jsou multibitové posunové registry, paměťové jednotky a určité typy čítačů.

V těchto aplikacích poskytují západky SR stabilní zadržování dat a mohou rychle reagovat na změny v externích signálech, což zajišťuje efektivní provoz celého elektronického systému.

Další kritická aplikace SR západků je v detekci chyb a korekční logika v digitálních obvodech.Vzhledem k jejich schopnosti držet stabilní stav mohou sledovat změny stavu systému a rychle se vrátit k předdefinovanému bezpečnému stavu po detekci anomálie.Tato funkce je obzvláště cenná v systémech s vysokou relikovatelností, jako jsou Aerospace a zdravotnické prostředky.

Symbol západky SR

Pochopení jeho symbolu a struktury je zásadní pro uchopení jeho činnosti a praktického použití.V obvodových diagramech má západka SR obvykle dva hlavní vstupní porty označené S (sada) a R (resetování).Tyto vstupy řídí stav výstupu západky, běžně reprezentovaný jako Q. Některé vzory také mají inverzní výstup, označený Q ', který poskytuje opačný stav Q.

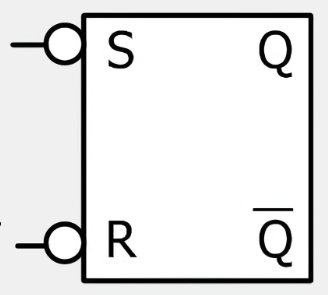

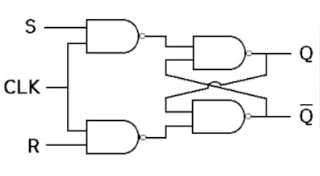

Obrázek 3: Symbol západky SR

Západka SR je často reprezentována pravoúhlým symbolem se vstupy S a R a výstupem Q. V některých případech je také zobrazen výstup q '.Toto jasné značení umožňuje návrhářům obvodů rychle identifikovat funkci komponenty a její roli ve větším obvodu.

Společná varianta západky SR zahrnuje vstup hodin (CLK).Vstup CLK zajišťuje, že změny stavu dochází v synchronizaci se signálem hodin, což umožňuje přesné ovládání načasování.V tomto nastavení, i když je aktivován S nebo R, se stav západky aktualizuje pouze tehdy, když signál CLK splňuje specifické podmínky, obvykle na stoupající nebo klesající hraně.To zabraňuje chybám způsobeným závady vstupního signálu nebo nezamýšlenými změnami.

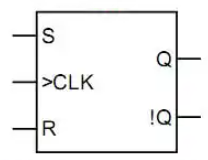

Obrázek 4: Symbol západky SR s hodinami

Symbol západky SR zahrnuje vstupy S, R a CLK uvnitř obdélníku.Tato standardizovaná reprezentace pomáhá návrhářům pochopit funkčnost západky a její požadavky na načasování.Například ve vysoce výkonných výpočtových nebo komplexních systémech přenosu dat zajišťuje pečlivé ovládání CLK uložena a přenášena přesně v každé fázi zpracování, což optimalizuje celkový výkon a spolehlivost systému.

Přesná kontrola vstupů západky SR je důležitá, zejména při navrhování vysokorychlostní a velké kapacitní paměti nebo dočasných dat.Navrhováním logických obvodů pro správu aktivace S a R lze dosáhnout komplexních funkcí, jako je načítání dat, zúčtování nebo resetování stavu.Přesná kontrola signálu CLK zajišťuje, že všechny datové operace sledují předdefinovanou sekvenci časování, což výrazně zvyšuje účinnost systému a schopnost zpracování dat.

Hluboké porozumění symbolu a struktuře SR Latch pomáhá nejen při navrhování a řešení problémů správného obvodu, ale také při provádění komplexních digitálních logických operací a zlepšování výkonu systému.To je zvláště kritické v aplikacích, které vyžadují vysokou spolehlivost a přesnou kontrolu, jako jsou letecké a zdravotnické prostředky.

Typy západků a jejich pracovní principy

Západky jsou základní komponenty v elektronickém designu a nabízejí rozmanité funkce a široké aplikace.Hlavními typy západků jsou západky SR a západky D, z nichž každá má jedinečné operace a případy použití.

SR západka

Západka SR, nebo nebo západka setu, je základní úložné zařízení ovládané dvěma vstupy, S (sada) a R (resetováním).

Když vstup S dostane vysoký signál, výstup Q je vysoký, což naznačuje, že jsou nastavena data.Když vstup R dostane vysoký signál, výstup q se stane nízkým, což ukazuje na resetování dat.Pokud jsou oba vstupy S a R současně, západka vstoupí do nedefinovaného stavu, což způsobuje potenciální nestabilitu výstupu.Této podmínce je třeba zabránit v designu.Přímá reakce SR Latch na vstupní signály je užitečná v situacích vyžadujících rychlou reakci.

D Západka

Západka D, známá také jako západka pro datovou západku nebo průhledná západka, nabízí složitější ovládání s datovým vstupem D a signál CLK.

Obrázek 5: D Latch

Obrázek 6: D Symbol západky

Když je CLK vysoká, výstup Q následuje vstup D, což umožňuje volně procházet data skrz západku.Když CLK klesne, proudová hodnota D je uzamčena a výstup q zůstává konstantní až do dalšího signálu CLK.Tento mechanismus způsobuje, že D západka ideální pro dočasné ukládání dat pro synchronizaci různých rychlostí zpracování v systému.

Západky SR a D mají bezkonkurenční roli při ukládání dat a logice státu stroje.Vzhledem k jejich přímé reakci na úrovni vstupu jsou západky nezbytné při navrhování asynchronních obvodů.Poskytují životně důležité funkce pro složité převody dat a systémy správy energie a účinně ukládají informace o stavu, aby zajistily stabilní provoz.Správné použití těchto západků může výrazně zlepšit spolehlivost a účinnost obvodů, což je v moderních elektronických systémech nezbytné.

Tabulka pravdy západky SR

Obrázek 7: Sr Nand západka

|

S |

R |

Q |

Q ' |

Poznámka |

|

0 |

0 |

1 |

1 |

Zakázáno |

|

0 |

1 |

1 |

0 |

SOUBOR |

|

1 |

0 |

0 |

1 |

Resetovat |

|

1 |

1 |

Q |

Q ' |

Udržet |

Schéma 1: TABLE TABLE TABLE SR západky pomocí bran Nand

Obrázek 8: Sr ani západka

|

S |

R |

Q |

Q ' |

Poznámka |

|

0 |

0 |

Q |

Q ' |

Udržet |

|

0 |

1 |

1 |

0 |

Resetovat |

|

1 |

0 |

0 |

1 |

SOUBOR |

|

1 |

1 |

0 |

0 |

Zakázáno |

Schéma 2: Tabulka pravdy SR západky pomocí ani brány

Nyní bereme tabulku pravdy západky SR pomocí ani brány jako příkladu, abychom pochopili význam tabulky pravdy západky SR.

Vstupní a výstupní stavy

Oba S a R jsou 0: Západka zůstává ve svém současném stavu.Výstup q zůstává stejný, ať už je to 0 nebo 1.

S je 0 a R je 1: západka resetuje a vynoří výstup q na 0.

S je 1 a r je 0: sady západky, díky čemuž je výstup q rovný 1.

Oba S a R jsou 1: Tato podmínka je neplatná nebo nedefinovaná, často označována jako „zakázaný“ stav v západce SR.V tomto případě se Q a Q 'rovnají 0, což vede k nejednoznačnému výstupu.

Když jsou S a R obě 0, západka nedělá nic a jednoduše drží svou současnou hodnotu.To je užitečné pro udržování stavu bez změn.

Když je S 0 a R je 1, západka je výslovně řečeno, aby resetovala, ujistěte se, že Q je 0 bez ohledu na jeho předchozí stav.Toto je přímý způsob, jak vyčistit západku.

Když je S 1 a R je 0, západka je nastavena a zajistí, že se Q stane 1. Takto ukládáte „1“ do západky.

Pokud jsou S a R oba 1, stav není povolen, protože způsobuje, že oba výstupy jsou 0, což je protichůdné a nespolehlivé.Návrháři se musí této podmínce vyhnout, aby zajistili stabilní provoz.

Výhody a nevýhody západků

Západky se široce používají v designu digitálního obvodu kvůli jejich jednoduchosti a nízkých nákladech.Tyto vlastnosti umožňují západkům pracovat při vysokých rychlostech s nízkou spotřebou energie, což z nich činí ideální pro vysokorychlostní digitální systémy.Například v souborech registru procesorů mohou západky rychle ukládat a načíst data, což výrazně zvyšuje rychlost a účinnost zpracování.

Výhody západků

Jednoduchost a nákladová efektivita: Západky jsou přímé komponenty, které jsou levné implementovat v digitálních obvodech.

Vysoká rychlost a nízký výkon: Jejich design umožňuje rychlý provoz s minimální spotřebou energie, což je kritické ve vysokorychlostních digitálních systémech.

Účinnost při zpracování dat: V aplikacích, jako jsou soubory registru procesorů, západky poskytují rychlé ukládání a vyhledávání dat, což zvyšuje celkový výkon systému.

Nevýhody západků

Navzdory jejich výhodám mají západky pozoruhodná omezení v určitých návrzích a aplikacích.

Nepředvídatelné chování v asynchronních vzorcích: Bez kontroly signálu hodin se západky mohou chovat nepředvídatelně.V západkách SR, pokud jsou vstupy sad (S) i resetování (r) současně vysoké, výstup se nedefinuje, což vede k nestabilitě.To je problematické při kontrole v reálném čase nebo v oblasti kritiky bezpečnosti, kde je zásadní spolehlivý výstup.

Komplexní návrh načasování: Navrhování s západkami vyžaduje pečlivé načasování.Inženýři musí odpovídat za zpoždění šíření signálu a podmínky rasy, aby se zabránilo chybám načasování.Nesprávný návrh může vést ke změnám dat před stabilizací signálu hodin, což způsobí korupci dat nebo nesprávné zachycení dat.To vyžaduje hluboké porozumění analýze načasování a chování obvodů.

K řešení těchto výzev lze použít konkrétní techniky a strategie návrhu:

Synchronizační mechanismy: Přidání synchronizačních mechanismů může pomoci zvládnout asynchronní vstupy a zmírnit nepředvídatelné chování.

Vlastní správa hodin: Implementace strategií správy přizpůsobených hodinek může zajistit, aby byla data správně a ve správné době zakončena.

Použití nástrojů EDA: Modern Electronic Design Automation (EDA) Nástroje nabízejí pokročilou analýzu a optimalizační schopnosti.Tyto nástroje pomáhají předvídat a vyřešit problémy s načasováním a synchronizací během fáze návrhu, což zvyšuje spolehlivost a výkon digitálních systémů pomocí západků.Pomáhají návrhářům při brzy identifikaci potenciálních problémů a zajišťují, aby konečný produkt fungoval spolehlivě za různých podmínek.

Praktické aplikace SR Západky

SR Západky, známé svou schopností rychle a spolehlivě udržovat stav, se široce používají v různých elektronických systémech.Vynikají ve scénářích vyžadujících dočasné ukládání dat nebo udržení stavu.

Dočasné ukládání dat

Západky SR se často používají v paměti mezipaměti k dočasnému ukládání dat.To umožňuje systému rychle přístup k často používaným datům, což výrazně zvyšuje schopnosti zpracování dat a účinnost rozsáhlých procesorů.

Soubory úložiště

V procesorech umožňují západky SR rychlé ukládání a vyhledávání dat v souborech registru, zvyšují rychlost zpracování a celkový výkon systému.

Udržování kontrolních signálů

V systémech digitálních řídicích systémů jsou SR západky užitečné při udržování stavu určitých kontrolních signálů, dokud vnější podmínky nebo logika systémů neznamená změnu.Pomáhají také při udržování států v systému a zajišťují konzistentní výkon v operacích, které vyžadují přesnost a spolehlivost.

Spouštěcí a pultové obvody

Žabky na bázi SR Latch se běžně používají v obvodech vyžadujících synchronizovaný provoz, jako jsou digitální hodiny a časovače.Ovládají počet pulzů a zajišťují přesné časové míry a spolehlivý výkon.Tyto obvody se spoléhají na západky SR, aby udržely přesné počty, což usnadňuje načasování a sekvenování v digitálních systémech.

Mechanické interakce

Západky SR jsou účinné při eliminaci mechanického odrazu ve spínačích.K mechanickému odrazu dochází, když přepínač generuje rychlé, opakující se změny signálu v důsledku špatného kontaktu.Západky SR stabilizují výstupní signál a zabraňují chybám způsobeným hlučnými signály.

SR Flip-Flop

SR Flip-Flop, často nazývaný překlopení setu s rozložením okraje, se skládá ze dvou vzájemně propojených západků SR.Tato struktura duálního západku umožňuje reagovat na specifické okraje signálu hodinového signálu (buď stoupající nebo padající), aby změnil svůj stav.Toho je dosaženo speciální logickou kontrolou mezi západky.Výstup první západky se stává součástí vstupu pro druhou západku a výstup druhé západky zase ovlivňuje první západku a vytvoří vzájemnou zpětnou vazbu.

Obrázek 7: SR Flip-Flop

SR Flip-Flop změní stav přesně na stoupající nebo klesající hraně signálu hodinového signálu.Zápasová zpětná vazba mezi dvěma západky SR zajišťuje, že překlopení mění stav pouze v reakci na hranu hodin a poskytuje stabilní a spolehlivý výstup.

V mikroprocesorech a procesorech digitálních signálů se pro vzorkování a ukládání dat používají žabky SR.Zachycují a stabilizují data na specifikovaných hrankách hodin, což zajišťuje spolehlivé následné zpracování a analýzu dat.

Mechanismus spouštění okrajů pomáhá vyhnout se podmínkám závodu, kde různé části obvodu mohou měnit stav současně bez synchronizace, což potenciálně vede k nestabilním nebo nesprávným výstupům.Překlopení SR jsou zásadní při implementaci specifické logiky komunikačního protokolu, jako je synchronizace rámců a detekce chyb.Jejich stabilita a rychlá doba odezvy pomáhají udržovat kvalitu přenosu dat a spolehlivost systému.

Zakázané státy v západkách SR a SR žabky

Při navrhování západků SR a žabků SR pomocí NAND a NOR bran musíme všichni věnovat pozornost řízení a vyhýbání se inhibičním stavů.Zakázaný stav nastává, když jsou vstupy sady (S) i resetování (R) současně vysoké (pro brány NAND) nebo nízké (pro brány).Tato kombinace vede k neurčitému výstupnímu stavu, protože výstup závisí na předchozím stavu obvodu, což je nepředvídatelné.

Zakázané státy v západkách Nand Gate SR

Když jsou oba S a R nízké, oba výstupy jsou vysoko, což porušuje charakteristiku doplňkové výstupu západky.To má za následek neurčitý stav.

Zakázané státy v západkách SR

Když jsou oba S a R vysoké, oba výstupy klesnou a také vytvářejí neurčitý stav.To může vést k nepředvídatelnému chování v obvodu.

Praktické přístupy k zamezení zakázaných států

Přidání logiky kontroly

Pomocí dalších logických bran pro sledování stavů S a R. Pokud oba vstupy směřují směrem k zakázanému stavu, automaticky upravte jeden vstup, aby se zabránilo neurčitému stavu.Tím je zajištěno, že výstupy zůstanou stabilní a předvídatelné.Implementujte logickou bránu, která zasáhne, když jsou S a R vysoké (nebo nízké), a nastaví jeden vstup tak, aby udržoval platný stav.

Simulace softwaru a testování hardwaru

Proveďte důkladné simulace softwaru za účelem identifikace potenciálních zakázaných států za různých provozních podmínek.To umožňuje návrhářům napojit a opravit logické chyby před fyzickou implementací.Proveďte rozsáhlé testování hardwaru, abyste ověřovali, že obvod zpracovává všechny vstupní kombinace správně.Tento krok pomáhá zajistit, aby západka nebo flip-flop fungovala spolehlivě ve scénářích v reálném světě.

Závěr

Všestrannost a spolehlivost západků SR podtrhuje jejich význam při návrhu digitálního obvodu.Zkoumáním nuančního chování SR západků prostřednictvím jejich symbolických reprezentací, tabulek pravdy a praktických aplikací získáme komplexní porozumění jejich fungování a důležitosti.Přes potenciální úskalí nedefinovaných států v asynchronních návrzích může strategická implementace kontrolní logiky a rozsáhlé simulace tyto rizika zmírnit.Nástroje Advanced Electronic Design Automation (EDA) dále zvyšují spolehlivost a výkon obvodů zahrnujících SR západky předpovídáním a řešením problémů s načasováním a synchronizací.Ať už se používají při dočasném ukládání dat, údržbu kontrolního signálu nebo detekci chyb, SR Západky se ukázaly jako základy při vytváření robustních a efektivních digitálních systémů.Jejich role ve vysokorychlostní paměti a synchronním zpracování dat ve složitých aplikacích je příkladem jejich trvalého významu.Jak technologie postupuje, principy upravující SR západky nadále informují a inspirují inovace v digitální elektronice a zajišťují, aby tyto základní komponenty zůstaly nedílnou součástí vývoje sofistikovaných a spolehlivých elektronických zařízení.

Často kladené otázky [FAQ]

1. Co je to západka SR?

Západka SR nebo západka se set-reset je základní binární úložný prvek používaný v digitálních obvodech.Jedná se o asynchronní obvod, což znamená, že pracuje bez signálu hodin a spoléhá se na přímou kontrolu svých vstupů ke změně stavů.

2. Jaká je funkce SR v logice?

V logice řídí vstupy SR (Set-Reset) stav západky.

3. Jaký typ logické brány používá západka SR?

SR západka obvykle používá ani brány nebo branky.V západce SR založené na bráně je výstup každé brány přiváděn zpět do vstupu druhého a vytvoří stabilní zpětnou vazbu.V západce SR založené na NAND se používá podobná konfigurace zpětné vazby, ale úrovně logiky jsou invertovány ve srovnání s západkou založenou na bráně.Obě konfigurace dosahují stejné základní funkce udržování binárního stavu na základě sady a resetování vstupů.

4. Jak funguje západka?

Západka funguje pomocí zpětné vazby k udržení výstupního stavu na základě poskytnutých vstupů.V západce SR řídí sada (S) a resetování (R) vstupy stav výstupu (Q).Když je nastavený vstup aktivován (vysoký), je výstup nastaven na vysokou (1).Když je aktivován resetovací vstup (vysoký), výstup je resetován na nízký (0).Smyčka zpětné vazby v designu západky zajišťuje, že jakmile je výstupní stav vytvořen, zůstává stabilní, dokud jej nezmění nový vstupní signál.

5. Jaká je nevýhoda s západkou SR?

Primární nevýhodou západky SR je nedefinovaný stav, ke kterému dochází, když jsou vstupy sady i resetování (R) současně vysoké.Tato podmínka vede k neurčitému výstupnímu stavu, který může způsobit nestabilitu a nepředvídatelné chování v digitálních obvodech.Tento „zakázaný“ stát je třeba zabránit v návrhu, aby bylo zajištěno spolehlivý provoz.

Západka SR, západka setu, asynchronní obvod, binární úložný prvek, digitální obvody, ani brány, bran Nand, zpětná vazba, vysoký stav, nízký stav, nedefinovaný stav, přímý ovládání, dočasné ukládání dat, přechodné držení výsledků,Detekce chyb, letecké aplikace, zdravotnické prostředky, návrh obvodů, západka SR, vstupní signály, symbol a struktura, vysokorychlostní paměť, datů, ovládání načasování, přesná kontrola, retence stavu, mikroprocesory, procesory digitálních signálů, vzorkování dat, data, data, data, data, data, data, data, data, data, data, data, data, data, údaje, data, datSkladování, spuštěné hrany, SR Flip-Flop, zpětná vazba pro blokování, podmínky rasy, logika komunikačního protokolu, synchronizace rámců, detekce chyb, závady signálu, automatizace elektronického návrhu, nástroje EDA, synchronizační mechanismy, vlastní správa hodin, chyby načasování, zpoždění propagace, prodloužení, propagační zpoždění,Podmínky rasy, složité převody dat, systémy řízení energie, mechanické odskoky, praktické aplikace, systémy digitálního řízení, logické brány, simulace softwaru, testování hardwaru, zakázané stavy, spolehlivost západky.