Inovativní průvodce žabky JK: Analýza tabulek pravdy, mechanismy a strategické aplikace

Tento článek zkoumá architekturu, provoz a rozmanité aplikace JK flip-flop, počínaje jeho základní strukturou a vztahy vstup-výstup, prostřednictvím podrobné operační mechaniky, až po její strategické implementace ve složitých digitálních systémech.Diskuse se rozšiřuje na rozlišení mezi varianty vyvolanými okrajem a úrovní a analyzuje jejich příslušné nástroje v synchronním a asynchronním prostředí.Katalog

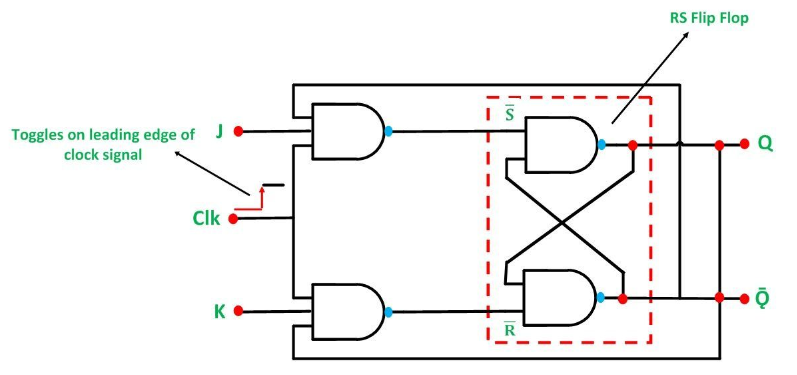

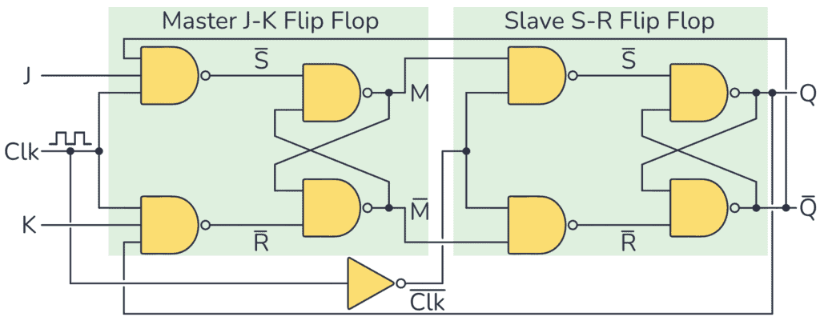

Obrázek 1: JK Flip-Flop

Základy JK Flip-Flop

Flip-Flop JK je základní součástí digitální elektroniky, která je navržena tak, aby ukládala jeden kousek informací.Staví na jednodušší SR Flip-Flop přidáním zpětné vazby, která pomáhá předcházet chybám známým jako „podmínky rasy“, kde se výstup stává nestabilní.

Tento flip-flop má dva hlavní vstupy, j (set) a k (reset) a dva výstupy: q a jeho doplněk, q '.Tyto výstupy nepřetržitě odrážejí aktuální stav a jeho opak, což umožňuje obvodu upravit a reagovat na vstupní změny v reálném čase.

Flip-Flop JK funguje specifickými způsoby na základě vstupních hodnot:

• Když jsou J a K 0: Flip-Flop drží svůj současný stav.Nedostanou se žádné změny.

• Když jsou J a K 1: Flip-flop přepíná jeho stav.Pokud q je 0, stane se 1;Pokud q je 1, přechází na 0. Tato přepínací akce je klíčovou funkcí, která odlišuje flip-flop JK od jednodušších návrhů.

• Když J je 1 a k je 0: Flip-flop nastaví svůj stav, takže Q rovná 1.

• Když J je 0 a K je 1: Překlopná flop se resetuje, takže Q rovná 0.

Provoz JK Flip-Flop

JK Flip-Flop hraje klíčovou roli v digitálních obvodech řízením paměti a načasování prostřednictvím koordinované reakce na vstupní signály a hodiny hodin.Jeho operace silně závisí na načasování vstupů J a K vzhledem k signálu hodin, který určuje, jak se výstupní stavy (Q a Q̅) mění.Tato synchronizace zajišťuje, že flip-flop se chová předvídatelně v různých aplikacích obvodu.Flip-flop spoléhá na NAND nebo NOR Gates, aby tyto změny státu zvládli.

Držení aktuálního stavu- Když jsou vstupy J a K nízké (0), převrácení udržuje svůj současný stav.Logické brány efektivně „zamknou“ výstupy a zajišťují, aby byl zachován předchozí stav (vysoký nebo nízký).Tato funkce držení je vážná v aplikacích, kde data musí zůstat stabilní, dokud není nutností konkrétní změna.

Nastavení vysokého výstupu (stav nastavení) -Když se objeví hodinový puls a J je vysoký (1), zatímco K zůstává nízký (0), logické brány se přizpůsobí tak, aby nastavily překlopení.To vede výstup Q do vysokého stavu (1).To je užitečné v situacích, kdy obvod potřebuje spustit vysoký výstup, například aktivaci zařízení nebo uložení „1“ v paměti.

Vymazání nízkého výstupu (stav resetování) - Pokud je j nízký (0) a k je vysoký (1) v době hodinového pulsu, přechody přechodu do resetovacího stavu a nutí Q klesnout (0).Tato resetování akce se často používá v obvodech, které po dokončení operace potřebují výchozí nebo vymazaný stav, jako je vymazání dat z paměti.

Přepínání výstupu - Jedinečná funkce flip-flopu se objevuje, když jsou J a K vysoké (1).Když dorazí hodinový puls, přepne se přepínač a přepíná výstup z jeho současného stavu do opačného stavu.Pokud je Q vysoká, je nízká a pokud je Q nízký, stává se vysokou.Tato funkce přepínače je naléhavá na aplikace, jako jsou čítače nebo zařízení, která se musí automaticky střídat mezi stavy.

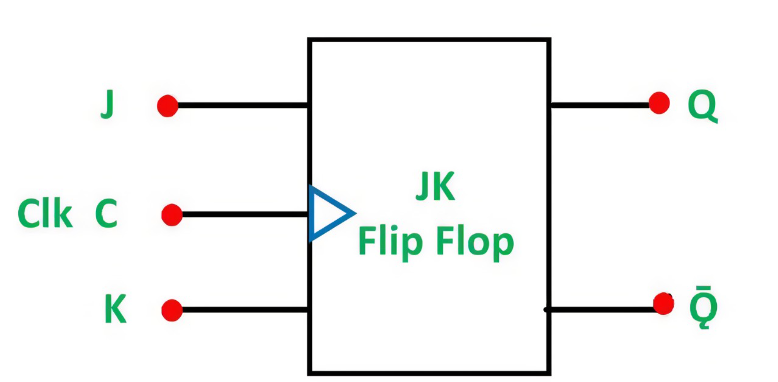

Obrázek 2: Tabulka pravdy JK Flip-Flop

Analýza tabulky pravdy JK Flip-Flop

Tabulka pravdy JK flip-flop je klíčovým nástrojem pro vizualizaci toho, jak reaguje na různé vstupní signály synchronizovaným s hodinovými impulzy.Tato tabulka pomáhá při navrhování i odstraňování problémů s digitálními obvody tím, že ukazuje, jak se výstupy flip-flopu mění na základě různých vstupních podmínek.

• J a K nízké (j = 0, k = 0): Když jsou oba vstupy 0, flip-flop drží svůj současný stav.Ať už je Q vysoký nebo nízký, zůstává nezměněn.To je pozoruhodné pro obvody, kde je požadována stabilní retence dat, jako jsou například prvky v paměti, kde je zachování současného stavu vhodné, dokud nebude spuštěna konkrétní změna.

• J High, K Low (j = 1, k = 0): Když J je 1 a K je 0, překlopná flop nastaví výstup q na vysokou (1).Tato podmínka nastavení je užitečná v aplikacích, které vyžadují přesný spouštěč pro aktivaci operace, jako je zapnutí zařízení nebo zahájení sekvence v logickém obvodu.

• j nízká, k vysoká (j = 0, k = 1): S j při 0 a k při 1 se flip-flop resetuje, což činí q nízké (0).Tato funkce resetování je vážná v systémech, které se musí vrátit do výchozího stavu, jako je při zúčtování dat nebo inicializace procesu.

• J a K vysoké (j = 1, k = 1): Když jsou oba vstupy vysoké, přepíná to jeho stav.Pokud je q vysoká, je nízká a pokud je q nízký, přepne se na vysokou.Toto přepínání chování je značné pro zařízení, která se musí střídat mezi státy, například ve frekvenčních dělicích nebo čítačích.

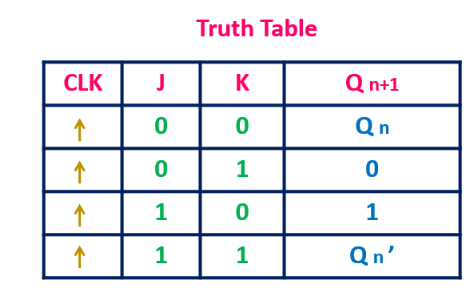

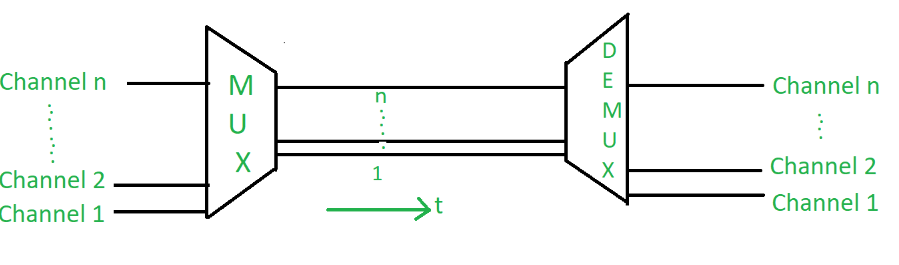

Obrázek 3: JK západka

Nahlédnutí do operace a použití západky JK

Západka JK pracuje podobně jako JK flip-flop, ale bez potřeby signálu hodin.Místo čekání na hranu hodin reaguje západka JK nepřetržitě na zadávání změn, takže je „úroveň citlivá“.To znamená, že pokud jsou vstupy (J a K) stabilní, výstup se změní v reálném čase a nabízí okamžitou zpětnou vazbu na základě vstupních podmínek.

Na rozdíl od JK Flip-Flop spuštěného okrajem, který aktualizuje jeho výstup, pouze pokud se změní signálu hodin (z nízkého na vysokou nebo naopak), JK západka okamžitě upravuje svůj výstup při posunu vstupů.Tato konstantní citlivost v reálném čase je cenná ve scénářích, kde je bezprostřední akce požadována bez zpoždění způsobeného synchronizací hodin.

Filtry šumu: V digitálních obvodech, které potřebují rychle odfiltrovat nežádoucí hluk, je okamžitá reakce JK západky na změny vstupu vlivné.Protože nečeší na hodinový puls, může upravit výstup, jakmile je detekován šum, což zabrání zpožděním korekce signálu.

Jednoduché paměťové prvky: Západka JK může sloužit jako základní paměťová jednotka v systémech, které nevyžadují složité, taktované ovládání.Vzhledem k tomu, že západka udržuje výstup stabilní, pokud se vstupy nezmění, účinně drží aktuální stav, který je užitečný pro obvody, které potřebují uchovávat informace bez režijních operací.

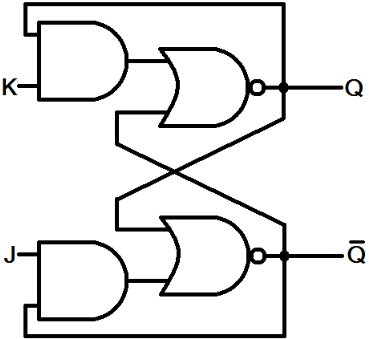

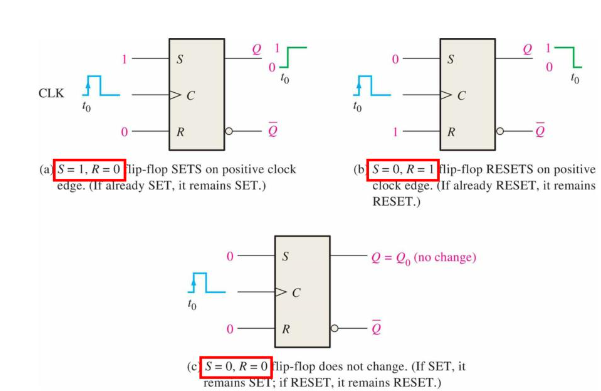

Obrázek 4: Analýza diagramu časování pro JK Flip-Flop

Analýza diagramu časování JK žabky

Schéma časování JK Flip-Flop poskytuje vizuální rozpis toho, jak výstup reaguje na různé vstupy, synchronizovaný s přechodem pulzů hodin.Tento diagram ukazuje vztah mezi hodinovým signálem (CLK) a vstupy (J a K) a jak společně ovlivňují výstupy (Q a Q ').Pomáhá mapovat chování flip-flopu napříč sekvenčními stavy, což usnadňuje pochopení jeho fungování.

Nejprve diagram zdůrazňují, že výstupy jsou aktualizovány pouze na rostoucích nebo padajících okrajích hodinového pulsu.Tato funkce, známá jako spouštění Edge, je dominantní k provozu JK Flip-Flop.Ukazuje, že i když se vstupy J a K změní, výstup zůstává nezměněn, dokud nedojde k okraji hodin, což zajišťuje předvídatelné a stabilní přechody.

Poté, když diagram mapuje změny vstupů J a K, vizuálně to demonstruje, jak každá vstupní kombinace ovlivňuje výstup. Například, když jsou J a K nízké (0), výstup drží svůj aktuální stav.Když je J vysoký a K je nízký, je nastaven výstup.Tato jasná vizuální reprezentace pomáhá uživatelům pochopit, jak flip-flop reaguje na různé vstupní kombinace v reálném čase.

Konečně, Schéma časování jasně ukazuje přechody mezi různými výstupními stavy, ať už držení, nastavení, resetování nebo přepínání.Každá změna státu je vázána přímo na vstupní podmínky a hranu hodin, což ukazuje vztah příčin a následků, který je ohnisko pro navrhování a odstraňování problémů.

Všestranné aplikace žabků JK

Klouby JK jsou jádrové komponenty v široké škále digitálních systémů, které jsou známé svou flexibilitou a spolehlivostí.Díky jejich schopnosti zvládnout složité logické operace je nutné v několika klíčových aplikacích, včetně:

Obrázek 5: Úložiště paměti

Překlopení JK se běžně používají k ukládání jednotlivých bitů dat, což z nich činí základní prvky v paměťových polích a registrech.Každý flip-flop drží jeden bit a zajišťuje spolehlivé ukládání dat, což je prospěšné při navrhování větších paměťových systémů.

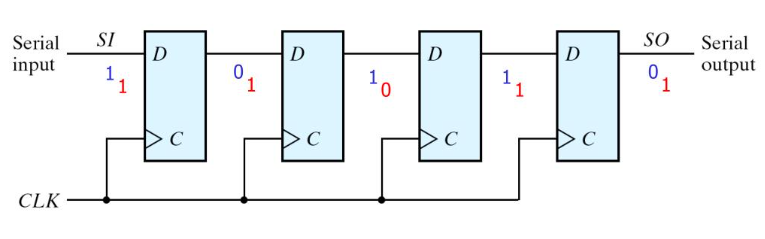

Obrázek 6: Čítače a registry posunu

Překlopení JK jsou dynamické v sekvenčních operacích.Oni se široce používají v pultech pro počítání událostí nebo impulsů a v směnových registrech pro převod sériových dat do paralelních formátů.Díky tomu jsou užitečnými při správě a manipulaci s údaji v různých fázích procesu, například v komunikačních systémech.

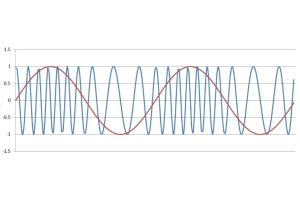

Obrázek 7: Divize frekvence

Při zpracování signálu se JK žabky často používají pro dělení frekvencí.Tím, že přepíná svůj stav s každým hodinovým pulsem, rozdělují frekvenci vstupního signálu a vytvářejí pomalejší a zvládnutelnější hodinový signál.To je pozoruhodné v aplikacích, jako je správa signálu hodin, kde je požadována kontrola načasování.

Obrázek 8: Synchronizace

Překlopení JK pomáhají synchronizovat více digitálních procesů zajištěním, že různé části systému spolupracují koordinovaným způsobem.Zajišťují, aby různé komponenty správně reagovaly na časované signály a udržovaly celý systém v synchronizaci.

Obrázek 9: JK Flip-Flop: Spuštěné na okraji a na úrovni

Různé typy žabků JK

JK žabky jsou k dispozici ve dvou hlavních typech: spuštěné na okraji a na úrovni, z nichž každá je navržena pro různé provozní požadavky.

Hrany spuštěné hrany JK: Změňte svůj stav pouze v konkrétních bodech - když přechody signálu hodinového signálu z nízké na vysokou (stoupající hranu) nebo vysokých na nízkou (klesající hranu).Tato charakteristika je činí ideální pro systémy, kde přesné načasování naléhavé.Protože změny stavu se vyskytují přesně na okraji hodin, tyto žabky zajišťují, že všechny aktualizace probíhají v synchronizaci s hodinovým pulsem.Toto předvídatelné chování je dynamické v pevně kontrolovaných prostředích, jako jsou digitální hodiny, registry a nejvíce sekvenční obvody.Zde je načasování každé změny vážné udržovat stabilitu systému a zajistit, aby byly operace synchronizovány.

Úroveň spuštěná JK Flip-Flops: Funguje jinak a reaguje na vstupní signál, pokud je hodinový signál na konkrétní úrovni - zda je vysoký nebo nízký.Nečekají na konkrétní přechod hodin.Místo toho, pokud vstup splňuje požadované podmínky, změní státy flip-flop.Toto chování způsobuje, že na úrovni vyvolané flip-flops se lépe hodí pro asynchronní systémy, kde vstupy nemusí být v souladu s běžným hodinovým pulsem.Poskytují flexibilitu v systémech, kde vstupy jsou nepředvídatelné nebo dorazí do nepravidelných intervalů, například v určitých úkolech zpracování signálu nebo monitorovacích systémech, které musí okamžitě reagovat na měnící se vstupy.

Výhody a nevýhody JK Flip-Flop

JK žabky nabízejí několik výhod, ale také přicházejí s některými kompromisy, které je třeba při navrhování digitálních systémů pečlivě zvážit.

|

Pros |

|

|

Všestrannost |

Žabky JK jsou vysoce flexibilní a mohou

být použit v různých digitálních obvodech, jako je ukládání paměti, čítače a

Řídicí systémy.Mohou přepínat, nastavit nebo resetovat na základě různých vstupů

podmínky, díky nimž jsou vhodné pro širokou škálu aplikací, které

Vyžadovat přesnou kontrolu nad přechody státu. |

|

Mechanismus samopravování |

Jedna z standoutů rysů JK

žabky je jejich vestavěná zpětná vazba, která pomáhá korigovat logické

státy dynamicky.Tato samoobsluha zajišťuje, že obvod zůstává

Stabilní během provozu, i když se vstupy rychle mění. |

|

Zmírnění podmínky rasy |

Na rozdíl od jednodušších žabků, JK žabky

jsou navrženy tak, aby zabránily podmínkám rasy

nestabilní kvůli konfliktním vstupním signálům.Tato schopnost udržovat

konzistentní výstup, dokonce i při rychlých a sekvenčních změnách vstupu, zlepšuje

spolehlivost obvodu. |

|

Nevýhody |

|

|

Komplexní design |

Žabky JK jsou komplikovanější než

Základní žabky.Jejich design vyžaduje další logické brány a vstup

monitorování, které může ztěžovat navrhování obvodu a

Odstraňování problémů, zejména v systémech, kde je preferována jednoduchost. |

|

Zpoždění šíření |

Vnitřní hradlování se používá ke správě stavu

Přechody zavádějí zpoždění v tom, jak lze zpracovat rychlé signály.V

Vysokorychlostní aplikace, toto zpoždění může ovlivnit celkové načasování a zpomalit

Výkon obvodu. |

|

Vyšší spotřeba energie |

Kvůli jejich složitosti a potřebě

Neustále sledujte vstupní podmínky, JK žabky konzumují více energie

ve srovnání s jednoduššími žabky.Ve větších systémech nebo citlivých na energii

Aplikace, tato vyšší poptávka po energii se může stát nevýhodou |

Obrázek 10: Master-Slave JK Flip-Flop

Dekódování Master-Slave JK Flip-Flop

Flip-Flop Master-Slave JK je navržen tak, aby vyřešil podmínku závodu nalezeného ve standardních žabkách JK pomocí dvoustupňového procesu pro efektivnější správu vstupů a výstupů.

První fáze, nazývaná hlavní fázi, zachycuje vstupní hodnoty, když signál hodin dosáhne konkrétního okraje, buď stoupající nebo padající.V tomto okamžiku jsou vstupní data uzamčena, což znamená, že další změny vstupů neovlivňují zachycený stav až do dalšího cyklu hodin.Tato fáze zajišťuje, že flip-flop zaregistruje správný vstup, aniž by byl ovlivněn jakýmikoli následnými změnami během stejného cyklu hodin.

Po dokončení hlavní fáze vstoupí do hry otrok.Tato fáze aktualizuje výstup na základě údajů zachycených hlavní fází, ale pouze na další hraně hodin.Oddělením zachycení vstupu od aktualizace výstupu zajišťuje fáze slave, aby výstup zůstal stabilní, dokud hlavní fáze vstup zcela nezpracovává.To zabraňuje jakýmkoli předčasným nebo nezamýšleným změnám výstupu během cyklu hodin.

Proč na konfiguraci hlavního otce záleží?

Dvoustupňový proces stabilizuje provoz flip-flopu JK a zabraňuje nežádoucím oscilacím nebo fluktuacím, ke kterým může dojít v jednodušších konfiguracích, zejména pokud jsou oba vstupy drženy vysoké.Oddělením zpracování vstupu z výstupu změny výstupu zajišťuje konfigurace hlavního otce, aby výstupy zůstaly předvídatelné a stabilní, a to i v situacích, kdy je načasování cenné.

Řešení závodu kolem stavu v JK žabky

Podmínky závodu se vyskytují v žabkách JK, když jsou oba vstupy, J a K, vysoké a hodinový signál zůstává aktivní příliš dlouho.To vede k nepřetržitému přepínání výstupů, což může způsobit nepravidelné chování a narušit spolehlivost obvodu.

Nastavení Master-Slave používá dvoustupňový proces k zabránění problémům s rasou.Hlavní fáze zachycuje vstupní hodnoty na okraji hodin a zamkne je. Stadiště slave aktualizuje výstupy na další hraně hodin a zajišťuje, že se výstup nemění, dokud nebudou vstupy plně zpracovány.Tento přístup účinně zabraňuje nekontrolovatelnému přepínání výstupu, i když vstupy zůstanou po delší dobu vysoké.

Další metodou, jak se vyhnout podmínkám závodu, je úprava doba trvání hodinového impulsu.Tím, že se hodinový puls zkracuje než zpoždění šíření flip-flopu, můžete zajistit, aby se stát neměnil více než jednou během stejného hodinového cyklu.To zabraňuje opakování přepínání flip-flopu během jediného cyklu a stabilizuje výstup.

Dynamika přepínání v JK žabkách

Přepínací chování JK flip-flop je do značné míry poháněno načasováním signálu hodinového signálu a vstupními úrovněmi (J a K).Stav změn flip-flop na základě vstupů přítomných na pozitivním okraji signálu hodin.V tomto nebezpečném okamžiku vyhodnocuje flip-flop vstupy a odpovídajícím způsobem aktualizuje svůj výstup.

Když signál hodin zasáhne stoupající hranu, přečtení JK přečte současné stavy vstupů J a K.V závislosti na jejich hodnotách bude flip-flop držet, nastavit, resetovat nebo přepínat jeho výstup.

Digitální hodiny: Přesnost je vše v digitálních hodinách a JK žabky pomáhají udržovat tuto přesnost tím, že zajišťují, že změny stavu se vyskytují pouze v přesných intervalech hodin.

Sekvenční logické testery: V systémech, které testují funkčnost logických obvodů, hrají JK flip-flops roli při ověřování, že každá složka správně reaguje na konkrétní časované signály.

Jiné časově citlivé systémy: V různých digitálních aplikacích, kde je načasování riskantní, jako jsou komunikační systémy nebo jednotky pro zpracování dat, JK Flip-Flop zajišťuje, aby se přechodové přechody vyskytly v synchronizaci s hodinami, což brání chybám načasování.

Závěr

JK Flip-Flop vyniká jako konečný prvek v designu digitálního obvodu a nabízí směs všestrannosti a přesnosti zoufalé pro širokou škálu aplikací od paměti po frekvenční dělení a synchronizaci digitálních procesů.Jeho schopnost zmírnit podmínky závodu prostřednictvím inovativních konfigurací, jako je uspořádání Master-Slave, podtrhuje její přizpůsobivost při řešení vlastních návrhových výzev.Stejně tak vážná role flip-flopu při zajišťování zajištění přesných přechodů státu zdůrazňuje jeho potřebnou povahu při vytváření a údržbě spolehlivých a efektivních digitálních systémů.Jak technologie postupuje, vyvíjející se návrhy a aplikace JK flip-flop jsou nadále klíčové při posunutí hranic digitální elektroniky směrem k sofistikovanějším a robustnějším architekturám.

Často kladené otázky [FAQ]

1. Jaké jsou aplikace JK flip flop?

Flip-flop JK se rozsáhle používá v digitální elektronice pro různé úkoly:

Aplikace načasování: Při připojení v určitých konfiguracích může sloužit jako prvek zpoždění nebo časovač.

Počtuty a registry: Tím, že přepíná svůj stav s každým hodinovým pulsem, se používá při navrhování různých čítačů a posunových registrů, které jsou v sekvenčních logických obvodech konečné.

Úložiště paměti: Poskytuje základní jednotku úložiště paměti, užitečná při ukládání bitů ve výpočetních aplikacích.

2. Jak funguje flip-flop JK s tabulkou pravdy?

JK Flip-Flop má dva vstupy (J a K) a hodinový signál.Jeho operace se liší v závislosti na vstupních stavech, synchronizovaných s hodinami:

• J = 0, K = 0: Výstup se nemění.

• J = 0, K = 1: Výstup se resetuje na 0.

• J = 1, K = 0: Výstup je nastaven na 1.

• J = 1, K = 1: Výstup přepíná (tj. Pokud to bylo 0, stane se 1 a naopak).

3. Co je to JK Flip Flop a funguje to?

Překlopení JK kombinuje vlastnosti žabků SR a T.Vyhýbá se „zakázanému“ stavu pozorovanému v žabkách SR efektivním použitím vstupů JK:

Stav flip-flopu je řízen vstupy J a K, které určují, zda by výstup měl držet, resetovat, nastavit nebo přepínat, synchronizovat se stoupajícím nebo klesajícím okrajem hodinového impulsu.

4. Jaké jsou aplikace západků a žabky?

Ukládání dat: Západky a žabky jsou pro ukládání dat vážné pro ukládání dat v rámci registrů a paměťových polí.

Divize frekvence: Používá se ve frekvenčních dělicích kvůli jejich schopnosti měnit stavy na okrajích hodin a polovinu frekvence s každou fází v sérii.

Státní stroje: Základní při navrhování konečných stavových strojů, které se používají k implementaci sekvenčních logických a řídicích obvodů.

Vození: Používá se ke stabilizaci signálů z mechanických spínačů a tlačítek, zajištění jednotlivých a čistých přechodů.

5. Na co se používají žabky?

Binární úložiště: Každá flip-flop ukládá jedno kousky dat, což z nich činí stavební bloky pro binární úložná zařízení.

Oddělovače hodin: Vydělují frekvenci vstupních hodin dvěma, užitečnými v digitálních hodinách a načasovacích aplikacích.

O nás

ALLELCO LIMITED

Přečtěte si více

Rychlý dotaz

Zašlete prosím dotaz, budeme odpovědět okamžitě.

JRC4558 OP-AMP: Funkce, specifikace a aplikace

na 2024/09/18

330 ohmových rezistorů a barevných kódů

na 2024/09/13

Populární příspěvky

-

Co je GND v obvodu?

na 1970/01/1 2953

-

Průvodce konektorem RJ-45: barevné kódy konektoru RJ-45, schémata zapojení, aplikace R-J45, datové listy RJ-45

na 1970/01/1 2505

-

Typy konektoru vláken: SC vs LC a LC vs MTP

na 1970/01/1 2095

-

Porozumění napětí napájení v elektronice VCC, VDD, VEE, VSS a GND

na 0400/11/9 1902

-

Porovnání mezi DB9 a RS232

na 1970/01/1 1767

-

Co je to baterie LR44?

Elektřina, ta všudypřítomná síla, tiše prostupuje každý aspekt našeho každodenního života, od triviálních gadgetů po život ohrožující lékařské vybavení, hraje tichou roli.Skutečně uchopit tuto energii, zejména to, jak ji ukládat a efektivně ji vydávat, není snadný úkol.Na tomto pozadí se tento článek zaměří na typ baterie mincí, která se může zdát na pov...na 1970/01/1 1715

-

Porozumění základy: odolnost proti indukčnosti a kapacitance

Ve složitém tanci elektrotechniky se trojice základních prvků zabírá v centru pozornosti: indukčnost, odpor a kapacita.Každý nese jedinečné rysy, které diktují dynamické rytmy elektronických obvodů.Zde se vydáme na cestu, abychom dešifrovali složitost těchto komponent, abychom odhalili jejich odlišné role a praktické použití v obrovském elektrickém orchestru.Indukčnost...na 1970/01/1 1665

-

CR2430 Baterie Komplexní příručka: Specifikace, aplikace a srovnání s bateriemi CR2032

Co je baterie CR2430?Výhody baterií CR2430NormaAplikace baterie CR2430CR2430 EkvivalentCR2430 vs CR2032Velikost baterie CR2430Co hledat při nákupu CR2430 a ekvivalentůDatový list PDFČasto kladené otázky Baterie jsou srdcem malých elektronických zařízení.Mezi mnoha dostupnými typy hrají mincovské buňky klíčovou roli, běžně se vyskytují v kalkulačkách, dálkovém ovladači ...na 1970/01/1 1573

-

Co je RF a proč ho používáme?

Technologie rádiové frekvence (RF) je klíčovou součástí moderní bezdrátové komunikace, což umožňuje přenos dat na velké vzdálenosti bez fyzických připojení.Tento článek se ponoří do základů RF a vysvětluje, jak elektromagnetické záření (EMR) umožňuje RF komunikaci.Prozkoumáme principy EMR, vytvoření a kontrolu signálů RF a jejich rozsáhlé použití.Článek s...na 1970/01/1 1553

-

CR2450 vs CR2032: Lze místo toho použít baterii?

Lithium manganové baterie mají určité podobnosti s jinými lithiovými bateriemi.Vysoká hustota energie a dlouhá životnost jsou vlastnosti, které mají společné.Tento druh baterie získal důvěru a laskavost mnoha spotřebitelů kvůli své jedinečné bezpečnosti.Drahé technologické gadgety?Malé spotřebiče v našich domovech?Rozhlédněte se a uvidíte je všude.Mezi tyto lithium...na 1970/01/1 1520