Podrobný průvodce plnému adderu

V oblasti digitální elektroniky a počítačového inženýrství představují doplňky jeden z nejdůležitějších stavebních bloků, klíčové ve výstavbě a funkčnosti složitějších aritmetických obvodů.Jako integrální komponenty aritmetické logické jednotky (Alu) usnadňují řadu výpočetních operací, od základní aritmetiky po komplexní logické úkoly nezbytné pro systémové operace.Jejich design, který se může lišit od jednoduchých polovičních přidavatelů po složitější plné doplňky, hraje klíčovou roli při zvyšování účinnosti a rychlosti zpracování v digitálních systémech.Tento článek se ponoří do podrobné architektury a funkčních nuancí různých typů doplňků, ilustruje jejich kritickou roli v moderní výpočetní technologii a zkoumá jejich operační logiku, obvody a aplikace v širším kontextu digitálního logického designu.

Katalog

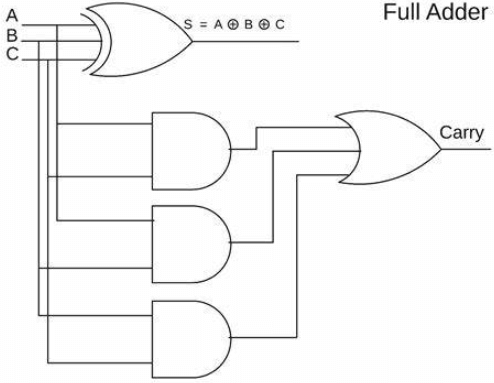

Obrázek 1: Plné přilnavosti

Adder je základní součástí elektronického inženýrství a digitálního logického designu a hraje ústřední roli ve složitějších počítačových systémech.V rámci aritmetické logické jednotky (ALU) se adder zpracovává řadu základních výpočetních úkolů.Účinnost a výkon celého procesoru jsou přímo ovlivněny návrhem a funkčností adderu.

V procesoru se adder používá nejen pro základní aritmetické operace, jako je přidání a odčítání, ale také se zapojuje do širší škály logických operací.Například při spuštění programů musí procesor často vypočítat nové adresy paměti.To se obvykle provádí přidáním nebo odečtením od aktuální adresy - úkol prováděného adderem.Řídí počet iterací smyček a celkový tok přírůstkem a snižováním čítačů.Ve složitějších aplikacích, jako je indexování tabulek, Adders rychle vyhledává data výpočtem ofsets.To je důležité pro systémy správy databází, konstrukci kompilátoru a rozsáhlé zpracování dat.Přidavatelé jsou také klíčoví při implementaci určitých technik mapování ve víceúrovňových mezipaměťových systémech pomocí aritmetických operací k určení polohy dat v mezipaměti, čímž se optimalizuje účinnost přístupu.

Technologicky jsou doplňky implementovány prostřednictvím různých návrhů obvodů, včetně paralelních, sériových a potrubních doplňků.Paralelní doplňky jsou upřednostňovány pro jejich schopnost zvládnout více číslic současně, takže jsou vhodné pro scénáře vyžadující rychlý výpočet.Na druhé straně sériové doplňky zpracovávají jeden bit na cyklus hodin a jsou ideální pro prostředí omezené zdroje nebo nízkoenergetickou prostředí.Přidávač potrubí rozdělují proces přidání do několika fází, z nichž každá zacházejí s součástí operace přidání.Tento návrh významně zvyšuje rychlost výpočtu, zejména ve vysoce výkonných výpočetních prostředích.

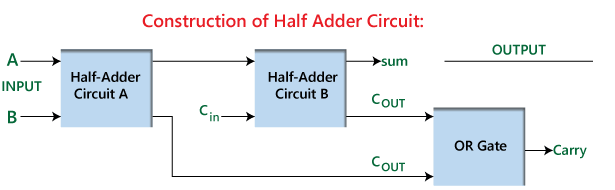

Okruh polovičního údržby je základní stavební blok v digitální elektronice, speciálně navržený pro přidání dvou jednotlivých binárních číslic.Tento obvod tvoří základ plného přilnavosti a je klíčem k porozumění složitějším návrhům logických obvodů.V polovině Adder existují dva primární vstupy, označené A a B, které představují Augend a dodatek.Toto nastavení mu umožňuje výpočet výstupu součtu a přenášení bez nutnosti přenosu vstupu z předchozích výpočtů.

Jádro polovičního adder se skládá ze dvou logických bran: brána XOR a an a brána.Brána XOR je zodpovědná za generování výstupu součtu.Funguje pod jednoduchým pravidlem, kde vydává 1, pokud je pouze jeden z jeho vstupů 1;Jinak vydává 0. The And Gate, na druhé straně, zpracovává výstup přenosu.Produkuje 1 pouze tehdy, když jsou oba její vstupy 1, dokonale se vyrovnává se základními požadavky na binární přidání.

Obrázek 2: Konstrukce polovičního adderu

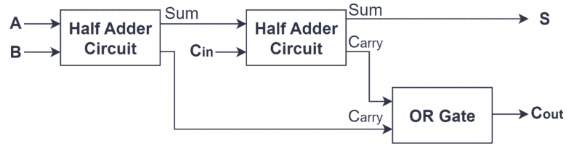

Tento efektivní a přímočarý design umožňuje polovičnímu semornému nejen provádět základní binární přidání nezávisle, ale také sloužit jako stavební blok pro vytvoření plného přikládače.Celý doplněk je zkonstruován kombinací dvou polovičních doplňků s další nebo bránou.V tomto nastavení převezme první poloviční adder počáteční přidanou úlohu a generuje předběžnou částku a přenášení.Druhá poločas se potom zpracovává přenos z prvního spolu s dalším vstupem do přenášení.Nakonec nebo brána sloučí tyto dva výstupy přenášení za účelem vytvoření konečného výstupu přenášení.Toto uspořádání zvyšuje funkčnost adderu a umožňuje jeho zvládnutí složitějších vícebitových přidaných úkolů, představuje rozšířenou aplikaci a důležitost polovičních doplňků v návrhu digitálního obvodu.

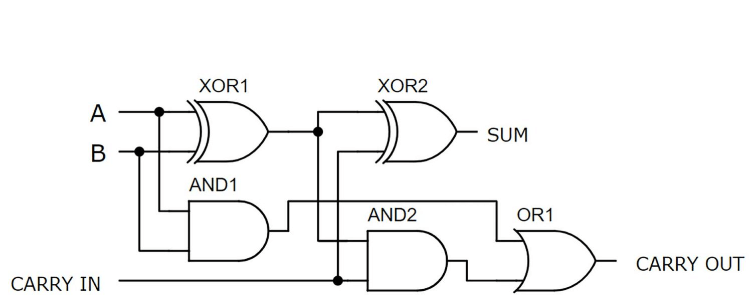

Celý doplněk je pokročilou součástí v digitálním logickém designu, vybaveném pro zpracování přidání tří jednobitových binárních vstupů, běžně označených jako A, B a Carry-in (CIN).Tento design umožňuje plnému adderu efektivně zpracovat komplexní binární přírůstky začleněním přenosu z předchozích výpočtů dolního řádu do jediné operace.

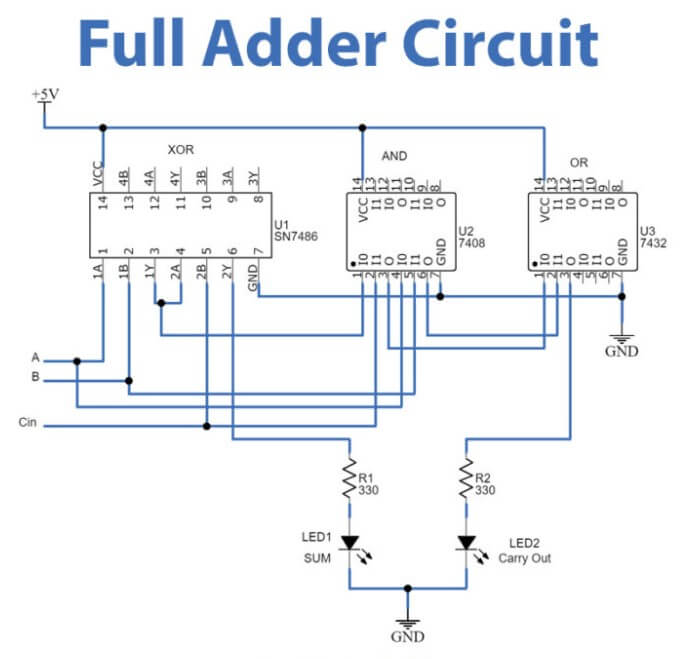

Obrázek 3: Celý obvod zkosení

Funkčně může plný doplněk vydat dvouciferný součet, což znamená, že jeho výstup se může pohybovat od 0 do 3, a může také vytvořit přenos (cout).K tomu dochází proto, že když jsou všechny vstupní bity nastaveny na 1 (A = 1, B = 1, CIN = 1), bude výstup součtu 1 (představující binární 01) a vygeneruje se přenos 1, což naznačuje, že to naznačujeDalší přenos musí být předán dalšímu vyššímu bitu.

Strukturálně, plný adder obecně sestává ze dvou polovičních doplňků a jedné nebo brány.První poločas se přijímá vstupy A a B a generuje počáteční součet a signál přenosu.Tato počáteční součet je poté napájena spolu s přenosem (CIN) do druhé polovině.Úlohou druhé poloviny Addera je přidat tuto součet z prvního poločasu do CIN, vytvořit další součet a nový výstup přenášení.Současně je výstup nošení z prvního poločasu a výstup přenášení z druhé poločasy se sloučen přes bránu OR, což vyvrcholí konečným přenášením (cout) plného leddera.Konstrukce této struktury zajišťuje, že plný doplněk účinně zpracovává šíření nosičů navíc k operacím, což je ideální pro provádění vícebitových binárních přírůstků.Konstrukce plného adderu tedy nejen zrychluje zpracování dat a zvyšuje účinnost, ale také zjednodušuje složitost implementace hardwaru prostřednictvím přímé kombinace logických bran, což z něj činí nepostradatelnou komponentu ve vícemístném přidání a aritmetické logické jednotce (Alu (Alu (Alu (Alu (Alu (Alu (Alu (Alu (Alu (Alu (Alu (Alu (Alu (Alu (Alu (Alu (Alu (Alu (Alu (Alu).

|

Parametry

|

Napůl zmizel

|

Plné přilnavosti

|

|

Popis

|

Polovina adder je kombinační logika

Obvod, který přidává dvě 1bitové číslice.Polovička produkuje součet dvou

vstupy.

|

Celý zkombinu je kombinační logika

Obvod, který provádí operaci přidání na třech jednombitových binárních číslech.

Celý doplněk vytváří součet tří vstupů a hodnoty přenášení.

|

|

Předchozí přenos

|

Předchozí přenos se nepoužívá.

|

Používá se předchozí přenos.

|

|

Vstupy

|

V polovině Adder jsou dva vstupní bity (a,

B).

|

V plném zmocnění jsou tři vstupní bity

(A, B, Cv).

|

|

Výstupy

|

Generovaný výstup je dvou bitů

a přenášet ze vstupu 2 bitů.

|

Generovaný výstup je dvou bitů

a přenést ze vstupu 3 bitů.

|

|

Používá se jako

|

Okruh polovičního údržby nelze použít

Stejným způsobem jako obvod s plným úchytkem.

|

Na místě lze použít plný obvod

polovičního obvodu Adder.

|

|

Funkce

|

Je jednoduché a snadné implementovat

|

Návrh plného zkosení není tak

Jednoduché jako poloviční adder.

|

|

Logický výraz

|

Logické výraz pro poloviční adder je:

S = A⊕B;C = a*b.

|

Logické výraz pro plné adder je:

S = a⊕b⊕cin;Cven= (a*b)+(cv*(A⊕B)).

|

|

Logické brány

|

Skládá se z jedné ex-nebo brány a jedné a

brána.

|

Skládá se ze dvou ex-nebo, dvou a bran,

a jedna nebo brána.

|

|

Aplikace

|

Používá se v kalkulačkách, počítačích,

Digitální měřicí zařízení atd.

|

Používá se při více bitových přírůstcích,

digitální procesory atd.

|

|

Alternativní jméno

|

Neexistuje žádné alternativní jméno pro polovinu

zmije.

|

Plný zmocnění je také známý jako zvlnění

zmije.

|

Schéma

1: Rozdíl mezi polovičním a plně

Tabulka pravdy plného adderu je klíčem k pochopení její operační logiky, která podrobně popisuje přesný vztah mezi kombinací binárních vstupů a jejich odpovídajícími výstupy.Tato tabulka demonstruje všechny potenciální vstupní scénáře a jejich výsledky, což z ní činí základní nástroj při navrhování a ověření digitálních logických obvodů.Celý adder zpracovává tři vstupy: A, B a přepravu (CIN), z nichž každý může být buď 0 nebo 1. To má za následek osm možných kombinací vstupů.

Pro každou z těchto kombinací zahrnují výstupy z plného adderu součet (součet) a přenos (cout).Součet je přidání modulo-2 (operace XOR) tří vstupů-A, B a CIN.K provedení dochází, když jsou alespoň dva ze vstupních bitů 1. To odráží schopnost plného doplňku zvládnout přenos v sekvenčních přidaných operacích, což zajišťuje přesnost ve vyšších bitových výpočtech.

Pro ilustraci zvažte vstupní scénář, kde jsou všechny vstupy 0 (A = 0, B = 0, C-in = 0).Výstupní součet bude 0 a přenos bude také 0, což naznačuje, že neexistuje žádná další součet nebo přenášení.Pokud je pouze jeden vstupní bit 1, například a = 1, b = 0, c-in = 0, výstupní součet bude 1 bez přenosu, což ukazuje, že není třeba přenášet přenos na vyšší bit.Když jsou dva vstupní bity 1, jako a = 1, b = 1, c-in = 0, je výstupní součet 0 (od 1+1 se rovná 2 v binárním a modulo-2 výsledkem 0), ale přenos-Out je 1, což ukazuje na přenos, který je třeba předat na další vyšší bit.K nejsložitějšímu scénáři dochází, když jsou všechny tři vstupní bity 1 (A = 1, B = 1, C-in = 1);Výstupní součet je 1 a je zde provedení 1, což naznačuje, že řízení přenosu může být také vyžadováno při ještě vyšších bitách.

|

A

|

B

|

Cv

|

S

|

Cven

|

|

0

|

0

|

0

|

0

|

0

|

|

0

|

0

|

1

|

1

|

0

|

|

0

|

1

|

0

|

1

|

0

|

|

0

|

1

|

1

|

0

|

1

|

|

1

|

0

|

0

|

1

|

0

|

|

1

|

0

|

1

|

0

|

1

|

|

1

|

1

|

0

|

0

|

1

|

|

1

|

1

|

1

|

1

|

1

|

Graf 2: TABULKA PLNĚNÍ ADDER PRAVDA

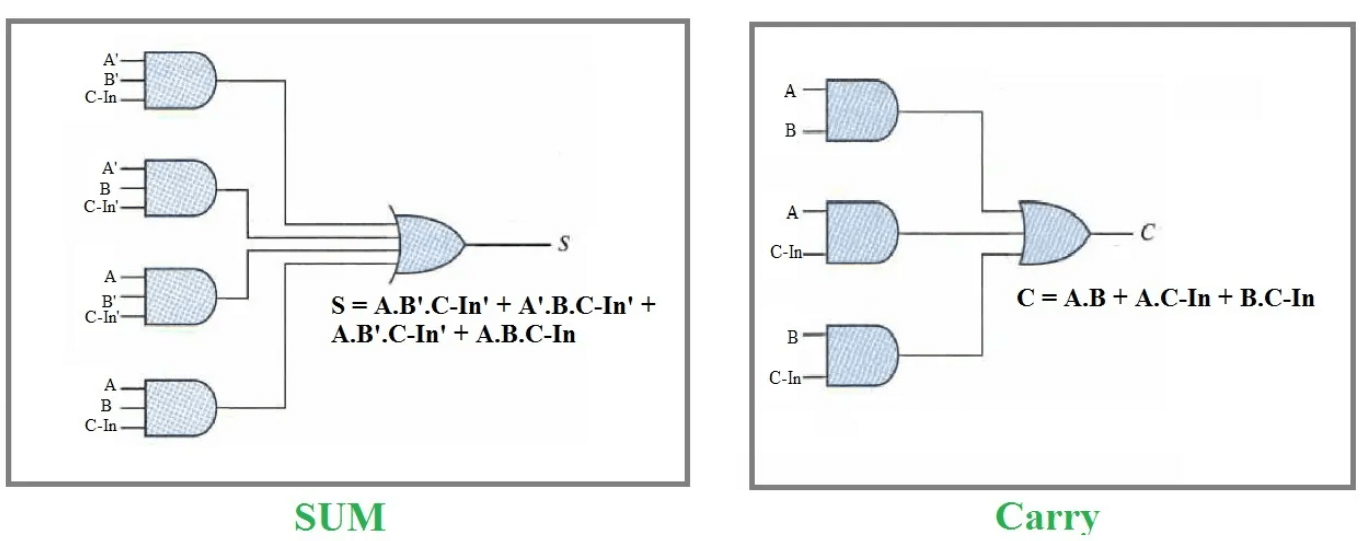

Pochopení celého adderu zahrnuje pitvu jeho funkčnosti pomocí tabulky pravdy, kde různé kombinace vstupních hodnot A, B a C-in vedou k výstupům součtu a cout.Abychom uchopili operaci, zjednodušujeme logické rovnice krok za krokem.

Logický výraz pro součet

Rovnice začíná odlišnými případy, kdy se částka rovná 1:

• A 'B' CIN + A 'B CIN' + A B 'CIN' + AB CIN

Tuto rovnici lze kondenzovat pomocí seskupení termínů s a bez CIN:

• CIN (A 'B' + AB) + CIN '(A' B + A B ')

Toto zjednodušení vede k snadnějšímu implementačnímu formuláři:

• CIN XOR (A XOR B)

Tato reprezentace ukazuje, že výstup součtu je v podstatě operací XOR mezi A, B a CIN, který zachycuje základní chování binárního přidání, kde SUM přepíná na základě lichého počtu.

Logika pro cout

Počínaje podmínkami, kde je generován nošení:

• A 'B CIN + A B' CIN + AB C-IN ' + AB CIN

Zjednodušení rovnice identifikujeme pojmy, které obvykle zahrnují generování přenosu:

• AB + B CIN + A CIN

Hledáte další metodu pro implementaci Cout, rovnici lze reorganizovat:

• AB + A CIN + B C-IN (A + A ')

To se rozšiřuje a rekombinuje, aby zachytilo všechny scénáře, kde jsou alespoň dva vstupy 1:

• AB CIN + AB + A C-IN + A 'B CIN

• AB (1 + CIN) + a C-in + a 'b Cin

• AB + A C-IN (B + B ') + A' B CIN

• AB + A B 'CIN + A' B CIN

• AB + CIN (A 'B + A B')

Konečná kompaktní formulář pro cout:

• AB + CIN (A XOR B)

Tato verze přenášení rovnice ukazuje, jak se Cout vyrábí buď, když jsou A a B 1, nebo když je jedna z A nebo B 1 spolu s přenosem, čímž se zapouzdřuje logiku potřebnou k řízení šíření přenášení ve více-Bit binární přidání.Tato zjednodušená logika je zvláště užitečná pro implementaci účinných digitálních obvodů.

Obrázek 4: Rovnice plného adderu

Implementace úplného obvodu Adder zahrnuje pečlivé sestavení dvou polovičních doplňků a brány nebo brány k vytvoření zařízení schopného efektivně zvládnout přidání tří jednobitových binárních vstupů.Toto uspořádání optimalizuje složitost obvodu a zajišťuje účinné i přesné výpočty.

Nejprve první polovina adderu vezme dva primární binární vstupy, A a B, které jsou hlavní číslice, které mají být přidány.Jeho klíčovým úkolem je vypočítat součet a počáteční přenos těchto dvou čísel.První polovina Adder zde přináší dva výsledky: počáteční součet (SUM1) a počáteční přenos (Carry1).SUM1 je odvozen z operace XOR A a B, což ukazuje, zda má celkový počet lichých počtu 1.Carry1, výsledek operace A a mezi A a B, ukazuje, zda jsou obě číslice 1, což vyžaduje přenos na další vyšší bit.

Poté se připojí k procesu druhá polovina Adder.Jako vstupy používá výstup SUM SUM1 a třetí vstup CIN (přenos z předchozího výpočtu).Druhá polovina Adder produkuje dva výstupy: konečný výsledek součtu (SUM2) a sekundární přenos (Carry2).Sum2, což je výsledek XOR SUM1 a CIN, představuje konečnou součet tří vstupů a zobrazuje agregovaný binární přidání.Carry2, vycházející z operace AS a operace mezi Sum1 a CIN, označuje přenos generovaný těmito komponenty.

Obrázek 5: Plný obvod Adder s použitím dvou polovičních adder

Nakonec, aby se dokončila design plného adderu, je nutná brána OR, aby zvládla výstupy přenášející se přenášejí1 a přenášením2 z obou polovičních doplňků.Tato nebo brána zajišťuje, že jakýkoli přenos generovaný během výpočtů je správně předán do konečného výstupu.Konečný výstup Adder je tedy výsledek (cout) výsledek přenosu1 a přenosu2.Začlenění této nebo brány zaručuje, že všechny potenciální přenosy jsou přesně vypočteny a předány na další úroveň v multibitových přídavných operacích, což zajišťuje integritu aritmetické operace napříč několika bity.

Úplné doplňky hrají nepostradatelnou roli v designu digitální logiky a nabízejí řadu výhod, díky nimž jsou nezbytné v různých scénářích výpočtu a zpracování dat.Mezi jejich primární výhody patří pozoruhodná flexibilita, rychlé rychlosti zpracování a efektivní řízení přenosu.Tyto vlastnosti způsobují, že plné doplňky jsou ideální pro provádění komplexních aritmetických operací a logických funkcí, zejména v aplikacích vyžadujících sekvenční vícebitové přidání.

Výhody

Flexibilita: Úplné přidávače vynikají ve své schopnosti zpracovávat více binárních vstupů (A, B a CIN) současně.Lze je také rozšířit do větších polí Adder, aby zvládli delší binární čísla.Tato škálovatelnost je důležitá pro budování vysoce výkonných aritmetických logických jednotek (ALUS), které musí provádět složité multibitové aritmetické a logické operace.

Rychlost: Díky jejich interní architektuře paralelního zpracování mohou plné doplňky dokončit přidání všech vstupů v jednom cyklu hodin a také se rozhodnout přenášet výstupy.Tato schopnost podporuje nepřetržité přidávání operací a je nezbytná pro zpracování dat v reálném čase v moderních mikroprocesorech a vysokorychlostní výpočetní zařízení.

Nevýhody

Úplní doplňky však také představují pozoruhodné nevýhody:

Složitost v návrhu a implementaci: Plně doplňky zahrnují více logických bran a víceúrovňové šíření, což činí jejich konstrukční komplex.Tato složitost nejen zvyšuje výrobní náklady, ale může také ovlivnit spolehlivost obvodů.

Problémy s zpožděním propagace: Propagace přenášení může projít několika logickými branami, z nichž každá přidává své zpoždění.To může omezit celkovou výpočetní rychlost během rozsáhlých operací, zejména v rozsáhlých počítačových systémech a při navrhování velmi velké integrace (VLSI) a vysokorychlostních procesorů.Zpoždění se může stát významným úzkým místem ve výkonu.

Aby se tyto problémy zmírnily, inženýři neustále zkoumají účinnější návrhy obvodů.Strategie zahrnují používání rychlejších logických technologií brány, optimalizace rozložení obvodů pro zkrácení délek cesty a vývoj pokročilých technologií, jako jsou doplňkové přidávání, aby se minimalizovaly zpoždění v šíření.

Úplné doplňky se rozsáhle používají v digitální logice, které jsou ceněny za jejich flexibilitu a efektivitu, což z nich činí ústřední pro mnoho úkolů výpočtu a zpracování dat.Jejich aplikace se rozprostírá od základních aritmetických operací po komplexní zpracování signálu a řízení systému.Zde je podrobný pohled na některé klíčové oblasti, kde jsou integrální plné doplňky.

Aritmetické obvody

Jedním z nejjednodušších využití plných doplňků je v aritmetických obvodech, kde provádějí binární přidání.Obzvláště klíčové při přidání multibitového čísla spravují úplné přidávání delší binární sekvence prostřednictvím kaskádování.V tomto uspořádání každý plný adder zpracovává sčítání pro svou bitovou polohu a přenášení z dolního bitů a poté projde nový přenos na další vyšším bitů.Tato kaskáda umožňuje komplexní vícebitové přidání v celé řadě číslic.

Zpracování dat

Plné doplňky také hrají klíčovou roli při pokročilých úkolech zpracování dat, jako je zpracování digitálního signálu (DSP) pro filtrování a Fourierovy transformace, kde jsou potřebné přesné a rychlé aritmetické operace.Navíc v oblasti informační bezpečnosti, včetně šifrování dat a detekce chyb a korekcí a korekčních algoritmů, jako jsou kontroly parity a generování kódu cyklické redundance (CRC), jsou pro provádění základních bitových operací zásadní.

Pulty

V digitálních čítačích jsou plní doplňky nepostradatelné pro implementaci funkcí přírůstků i dekrementů, zejména v modulárních a synchronních čítačích.Přesně spravují nese a půjčují si, aby zajistily přesné počítání.

Multiplexery (MUX) a DeMultiplexers (DeMux)

V multiplexerech a demultiplexerech hrají plnou přidavatelé rozhodující roli při výběru kanálů a distribuci dat.Zúčastní se logiky, která určuje, které kanály se používají pro vstup a výstup dat, a přijímají rozhodnutí na základě logických kontrolních signálů.

Technologie paměti

Při adresování paměti pomáhají plné přidávače generovat adresové signály pro dynamický přístup k paměťovým umístěním.To je obzvláště důležité v dynamické paměti náhodného přístupu (DRAM) a dalších systémech úložiště, kde plné doplňky podporují výpočty komplexních adres, aby se zvýšila účinnost přístupu k paměti.

Aritmetické logické jednotky (ALU)

A konečně, jako základní komponenty aritmetických logických jednotek v mikroprocesorech a procesorech digitálních signálů jsou zásadní plné doplňky.ALU zpracovává všechny aritmetické a logické operace, přičemž úplné doplňky zajišťují, aby data byla zpracována rychle i přesně.

Úplné doplňky mohou být konstruovány pomocí různých logických bran a konfigurací.Zde zkoumáme čtyři různé implementace a zdůrazňujeme jejich nastavení a provozní nuance.

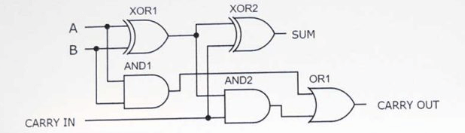

Plné doplňky postavené s XOR a nebo nebo brány

Obrázek 6: Plné doplňky postavené s XOR a nebo nebo logickými bránami

Tento příklad předvádí plný doplněk postavený na prkénku pomocí diskrétních tranzistorů.Konfigurace zahrnuje pět logických bran: dva XOR bran, dvě a brány a jedna nebo brána, vyžadující celkem 21 tranzistorů.Vstupy A a B jsou připojeny k levému hornímu prvku a dostávají napájení +5V.Tyto vstupy jsou řízeny pomocí dvou přepínačů.Dvě LED diody vlevo nahoře označují stavy vstupů A a B, zatímco dvě LED na pravé straně zobrazují výstupy.Rezistory použité v obvodu jsou všechny 2,2 khmy.Když jsou vstupy A a B zapnuté a přenosu je vypnuto, výstup ukazuje binární hodnotu 10, což představuje součet 2 (1 + 1 + 0 = 10).XOR Gates, postavené s prvními 12 tranzistory, zpracovávají primární souhrn, zatímco spodní polovina prkéle obsahuje a nebo bran pro operace přepravy, barevně kódované zapojení zvyšuje jasnost a odstraňování problémů.

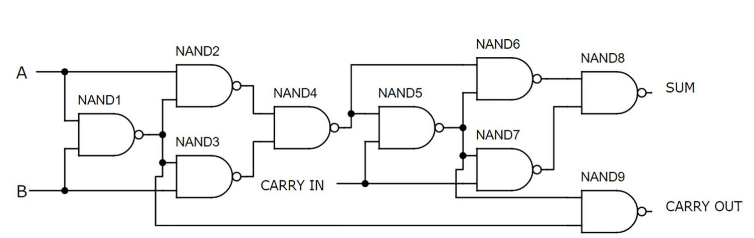

Plné přilnavosti pomocí bran Nand

Obrázek 7: Plné přilnavosti pomocí bran Nand

Tento plné adder využívá devět bran Nand, přičemž každá brána je vyrobena ze dvou tranzistorů, celkem 18 tranzistorů.Tato metoda patří mezi nejjednodušší a nejúčinnější způsoby, jak vytvořit plné přilnavosti pomocí diskrétních komponent.Všechny brány jsou sestaveny na horní polovině prkéle, zatímco spínače zabírají spodní polovinu.Funkčnost obvodu je demonstrována se vstupy A a B zapnutím a vypnutím, což má za následek výstupní binární hodnotu 10, což odpovídá desetinnému 2.

Plné zmizeč s brány

Obrázek 8: plné připevnění s bránami

Toto nastavení, z nichž každá vyžaduje dva tranzistory s devíti ani bránami, používá také celkem 18 tranzistorů.Budování plného přilnavosti s brány NOR nabízí dobrou alternativu, ale zahrnuje složitější zapojení ve srovnání s Gates NAND.Každý tranzistor v bránách Nor je uzemněn, s kolektory spojenými oranžovými propojovacími dráty, aby zajistily úhledné a organizované zapojení.Tato konfigurace je zobrazena s aktivovanými vstupy A a B a deaktivovaným přenosem, což vede k výstupům, kde je přenos aktivní a součet je vypnutý.

Během tohoto průzkumu technologie Adder, od základních polovičních doplňků po sofistikované designy plného doplňku, je zřejmé, že tyto komponenty jsou základem pro pokrok v digitální elektronice.Příklady provozních charakteristik a implementace poskytly zdůrazňování všestrannosti a efektivity doplňků v různých výpočetních prostředích.Zkoumáním struktury a funkce doplňků, zejména prostřednictvím jejich pravdních tabulek a charakteristických rovnic, získáme cenné poznatky o jejich schopnostech a omezeních.Tato znalost je nápomocná při rozvoji návrhu efektivnějších a rychlejších výpočetních systémů.Nakonec Addery nejen zjednodušují složité binární výpočty, ale také umožňují proliferaci technologie v oblastech tak rozmanitých, jako je zpracování dat, přidělování paměti a zpracování digitálního signálu.Jak se digitální technologie vyvíjí, probíhající zdokonalení a inovace v designu adder bude i nadále základním kamenem ve vývoji pokročilejších výpočetních architektur a zajistí, aby tyto základní komponenty zůstaly v srdci návrhu a implementace digitálního systému.

Často kladené otázky [FAQ]

1. Co je to plný obvod Adder?

Plným doplňkem je digitální obvod, který přidává tři binární bity k vytvoření součtu a výkonu přenášení.Je navržen tak, aby zvládl přidání tří vstupů: dva významné bity a jeden bit z předchozího přírůstku.To umožňuje, aby byl použit v následujících fázích k přidání vícebitových binárních čísel.

2. Kolik a nebo, XOR v plném přilnavosti?

Typický plné adder obsahuje:

Dvě brány XOR pro generování součtu.

Dvě a brány přispívat k výpočtu provedení.

Jedna nebo brána k dokončení výstupu pro přepravu.

3. Jaký je vstup přenášejícího v plném přilnavosti?

Vstup přenosu (CIN) v plném přilnavosti je přenosný bit z přidání předchozích nižších významných bitů ve vícebitovém binárním doplňku.Umožňuje celému adderu zvážit tento předchozí přenos při výpočtu aktuálního součtu a nového přenosu.

4. Proč místo polovičního smolovače používat plné složi?

Místo polovičního zkosení se používá plné složi, protože může přidat tři bity (včetně přenosu z předchozích přírůstků), což je vhodné pro odkazit dohromady a přidat vícebitová čísla.Poloviční držba může přidat pouze dva bity a nemá poskytování pro přepravu, což omezuje jeho použití na nejjednodušší formy binárního přidání bez sekvenčního šíření přenášení.